## Packing and Fusing Narrow-Width Vector Operations for Energy-Efficient SIMD

#### Miguel Eduardo Mateus Pinho

Thesis to obtain the Master of Science Degree in

#### **Electrical and Computer Engineering**

Supervisors: Prof. Nuno Filipe Valentim Roma Prof. Pedro Filipe Zeferino Aidos Tomás

#### **Examination Committee**

Chairperson: Prof. Teresa Maria Sá Ferreira Vazão Vasques Supervisor: Prof. Nuno Filipe Valentim Roma Member of the Committee: Prof. Nuno Cavaco Gomes Horta

July 2020

# **Declaration**

I declare that this document is an original work of my own authorship and that it fulfills all the requirements of the Code of Conduct and Good Practices of the Universidade de Lisboa.

# Acknowledgments

I want to start by thanking my family for their unwavering support and dedication: my parents, my brother, and my sister. I want to thank my supervisors, Prof. Nuno Roma and Prof. Pedro Tomás, for challenging me with this research opportunity, and for their constant feedback and advice, and thorough revisions. Had it not been for their demanding yet supportive attitude, this work would not be possible, and neither the personal growth it enabled. I had the luck of sharing the many challenges encountered in this thesis work with my colleague and friend João Mário, who always had some piece of advice. I also want to thank João Ramiro for his help in the thesis revision. The academic journey that now comes to an end would not have the same meaning without the friends from *SIIIIIIII* that accompanied me. I particularly treasure the companionship with Miguel Malaca and Pedro Mendes, with whom I overcame many a challenge (and who also helped with the revisions). This voyage was made even more significant by everyone I met at JUNITEC, where I found some of the most entrepreneur, dedicated, and motivated young people of my generation. Someone very special was also waiting there for me to meet, her name Sara Farias.

This work was partially supported by national funds through Fundação para a Ciência e a Tecnologia (FCT) under projects UIDB/50021/2020 and PTDC/EEI-HAC/30485/2017, and by funds from the European Union Horizon 2020 research and innovation programme under grant agreement No. 826647.

# Abstract

Application developers usually decide on the size of each variable data type by either considering its maximum range or simply by comfortably using larger data types. Since these represent maximum values (and not typical), the applications most often do not make full use of the bit-width offered by the processor integer arithmetic units. This wasted bit-width is especially relevant when using Single Instruction Multiple Data (SIMD) instructions, since the inefficient use of each arithmetic unit is multiplied by the number of vector elements. This (rather frequent) circumstance is herein exploited by proposing new run-time mechanisms to (i) efficiently handle narrow integer vector elements, by removing excess sign bits and packing these elements in a smaller vector, and (ii) agglomerate (fuse) multiple vector instructions pending in the execution queue of the processor, to simultaneously execute them on a single SIMD unit. When combined with clock and power gating techniques, the proposed approach provides a very significant reduction of the energy consumption in the SIMD units, by dynamically optimizing the execution of narrow-width integer vector computations, with low hardware overhead and no need for any changes in the application executable. Experimental results, based on a prototyping implementation supported on an ARM Cortex-A76 model, show a reduction of the dynamic and leakage energy consumption of the vector units of up to 54%, with either a negligible performance reduction or even some slight improvements of the execution time.

### **Keywords**

Narrow-width, SIMD Units, Clock and Power Gating, Energy Efficiency, General-purpose Processors

## Resumo

Os programadores de software normalmente decidem qual o tipo de dados de uma variável considerando o seu valor máximo esperado, ou simplesmente usando um tipo de dados com elevada precisão. Como os valores reais tendem a ser bastante inferiores a este valor máximo, grande parte da precisão das unidades aritméticas inteiras é desperdiçada. Em instruções vetoriais (ou SIMD) este desperdício da precisão do processador é ainda mais relevante, pois é multiplicado pelos vários elementos do vetor. Esta situação frequente é particularmente explorada neste trabalho através da proposta de novos mecanismos em hardware para (i) manipular elementos vetoriais inteiros de precisão reduzida, removendo os bits de sinal redundantes e compactando os elementos num vetor menor, e (ii) aglomerar (fundir) várias operações vetoriais à espera de execução na fila do processador, para execução simultânea numa única unidade de execução. Quando combinada com as técnicas de bloqueio do sinal de relógio e de alimentação, esta abordagem permite reduzir significativamente o consumo energético das unidades vetoriais, promovendo-se uma optimização dinâmica de cálculos vetoriais de inteiros, com uma penalização reduzida em termos de recursos de hardware e sem necessidade para quaisquer alterações nos ficheiros executáveis. Os resultados experimentais obtidos, baseados na prototipagem destes mecanismos com um modelo do processador ARM Cortex-A76, mostram uma redução do consumo de energia (dinâmica e estática) na unidade de execução vetorial de até 54%, com uma redução mínima no desempenho ou, até mesmo, em certas aplicações, com algumas melhorias ligeiras.

## Palavras Chave

Precisão Reduzida, Unidades SIMD, Técnicas de Bloqueio de Relógio e de Alimentação, Eficiência Energética, Processadores de Uso Geral

# Contents

| 1 | Intro | oductio | on la constant de la c | 1  |

|---|-------|---------|------------------------------------------------------------------------------------------------------------------|----|

|   | 1.1   | Motiva  | ation                                                                                                            | 1  |

|   | 1.2   | Objec   | tives                                                                                                            | 3  |

|   | 1.3   | Thesis  | s contributions                                                                                                  | 3  |

|   | 1.4   | Thesis  | s outline                                                                                                        | 4  |

| 2 | Bac   | kgrour  | nd and Related Work                                                                                              | 6  |

|   | 2.1   | Conte   | mporary GPP architectures                                                                                        | 7  |

|   | 2.2   | Power   | r efficiency in computer architectures                                                                           | 10 |

|   |       | 2.2.1   | Prevailing techniques for power efficiency                                                                       | 11 |

|   |       | 2.2.2   | Power gating unused functional units                                                                             | 12 |

|   |       | 2.2.3   | Reducing the SIMD units power dissipation                                                                        | 14 |

|   | 2.3   | Scala   | ble width datapaths                                                                                              | 15 |

|   |       | 2.3.1   | Software based techniques                                                                                        | 18 |

|   |       | 2.3.2   | Dynamic hardware-based approaches                                                                                | 19 |

|   |       | 2.3.3   | Scalable width structures                                                                                        | 20 |

|   |       |         | 2.3.3.A Functional units                                                                                         | 21 |

|   |       |         | 2.3.3.B Register file                                                                                            | 22 |

|   |       |         | 2.3.3.C Caches                                                                                                   | 24 |

|   | 2.4   | Summ    | nary                                                                                                             | 24 |

| 3 | Narı  | row-wi  | dth Opportunity in SIMD                                                                                          | 25 |

|   | 3.1   | Defini  | ng narrow-width in SIMD computations                                                                             | 25 |

|   | 3.2   | Optim   | izing vector computations in out-of-order processors                                                             | 28 |

|   | 3.3   | Profili | ng integer intensive applications                                                                                | 29 |

|   |       | 3.3.1   | Benchmarked applications                                                                                         | 30 |

|   |       | 3.3.2   | SIMD unit usage analysis                                                                                         | 31 |

|   | 3.4   | Envisa  | aged energy savings                                                                                              | 34 |

|   | 3.5   | Summ    | nary                                                                                                             | 36 |

| 4  | Arcl                                        | hitectural Mechanisms to Exploit Narrow-width                  | 37 |

|----|---------------------------------------------|----------------------------------------------------------------|----|

|    | 4.1                                         | Proposed Mechanisms                                            | 38 |

|    |                                             | 4.1.1 Width encoding                                           | 38 |

|    |                                             | 4.1.2 Packing narrow-width vector operands                     | 42 |

|    |                                             | 4.1.3 Fusing vector operations                                 | 45 |

|    |                                             | 4.1.4 Gating functional units                                  | 46 |

|    | 4.2                                         | Integration in conventional processor architectures            | 48 |

|    | 4.3                                         | Summary                                                        | 50 |

| 5  | Prot                                        | totyping and Experimental Workflow                             | 51 |

|    | 5.1                                         | Architectural simulation tools                                 | 52 |

|    | 5.2                                         | ARM ISA and the NEON vector extension                          | 55 |

|    | 5.3                                         | Implementation of the architectural changes                    | 56 |

|    | 5.4                                         | Traces and performance counters                                | 58 |

|    | 5.5                                         | Power modelling                                                | 60 |

|    | 5.6                                         | Experimental workflow                                          | 61 |

|    | 5.7                                         | Summary                                                        | 62 |

| 6  | Ехр                                         | perimental Evaluation                                          | 64 |

|    | 6.1                                         | Evaluation methodology                                         | 64 |

|    |                                             | 6.1.1 Considered configurations and benchmarks                 | 64 |

|    |                                             | 6.1.2 Evaluated metrics                                        | 66 |

|    | 6.2                                         | Experimental results                                           | 67 |

|    |                                             | 6.2.1 Energy and performance impact of the proposed mechanisms | 67 |

|    |                                             | 6.2.2 Design parameters exploration                            | 73 |

|    | 6.3                                         | Summary                                                        | 75 |

| 7  | Con                                         | nclusions and Future Work                                      | 76 |

|    | 7.1                                         | Conclusions                                                    | 76 |

|    | 7.2                                         | Future Work                                                    | 77 |

| Bi | bliog                                       | jraphy                                                         | 80 |

| Aŗ | Appendix A Considered Benchmark Datasets 86 |                                                                |    |

| Ap | pend                                        | dix B ARMv8 NEON Instructions                                  | 88 |

# **List of Figures**

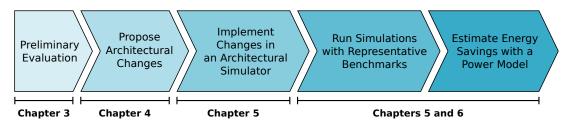

| 1.1  | Outline of the thesis work                                                          | 4        |

|------|-------------------------------------------------------------------------------------|----------|

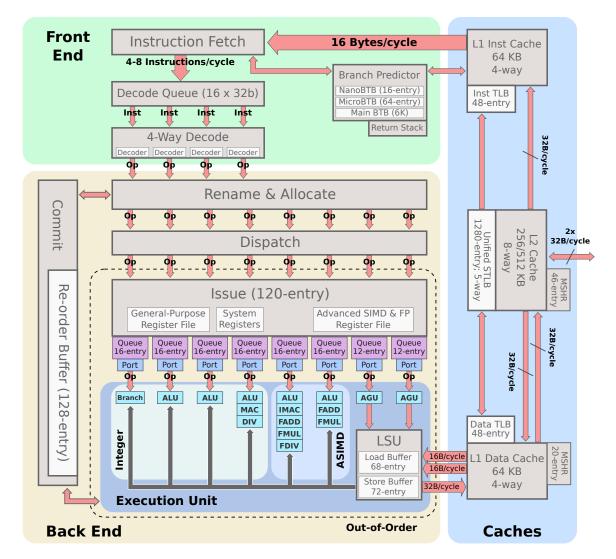

| 2.1  | Microarchitecture of the Arm Cortex-A76                                             | 7        |

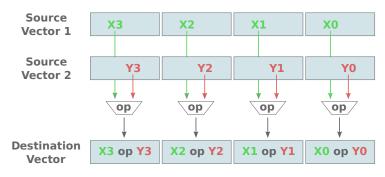

| 2.2  | SIMD execution model                                                                | 9        |

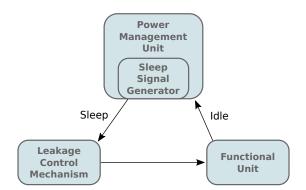

| 2.3  | Functional unit's power gating control mechanism                                    | 13       |

| 2.4  | Time-intervals in power gating                                                      | 14       |

| 2.5  | Narrow-width integer representation                                                 | 15       |

| 2.6  | Cumulative distribution of narrow-width values occurrence for SPEC2000              | 16       |

| 2.7  | Distribution of integer operations grouped by classes, for SPECint2000 applications | 17       |

| 2.8  | Operation fusing example                                                            | 19       |

| 2.9  | Cluster partitioned approach for narrow-width exploitation                          | 21       |

| 2.10 | Vectorized MAC design                                                               | 22       |

| 2.11 | Implementing 32-bit, 16-bit, and 8-bit operation modes in a 64-bit scalar MAC unit  | 23       |

| 3.1  | Width of a vector operation                                                         | 26       |

| 3.2  | Overview of vector operation modes in Arm NEON                                      | 20<br>27 |

|      |                                                                                     |          |

| 3.3  | Details of the SIMD execution engine in the out-of-order microarchitecture          | 29       |

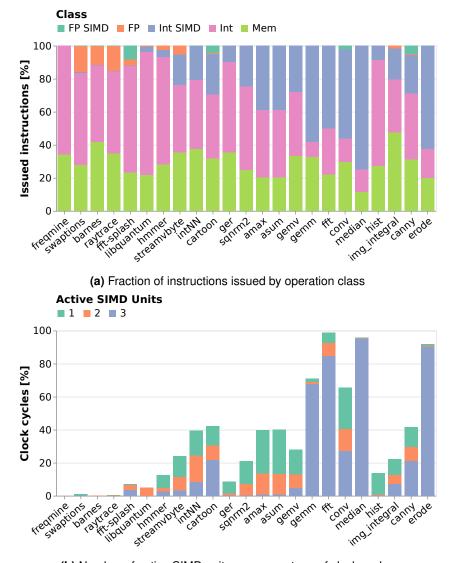

| 3.4  | Evaluation of the usage of the SIMD unit for the selected benchmarks                | 32       |

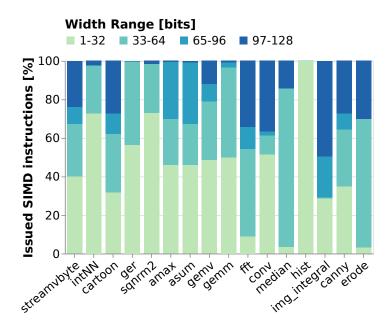

| 3.5  | Analysis of the width required by integer vector operations                         | 33       |

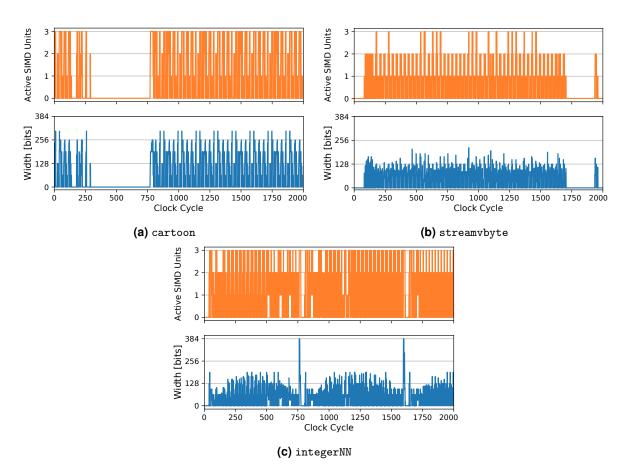

| 3.6  | Execution samples for the mini-apps                                                 | 34       |

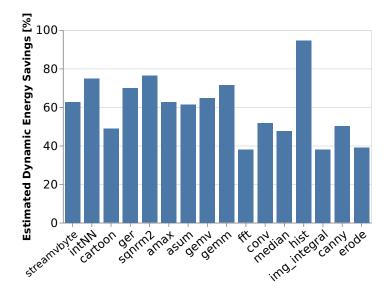

| 3.7  | Maximum expected dynamic energy savings                                             | 35       |

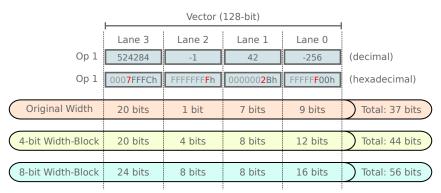

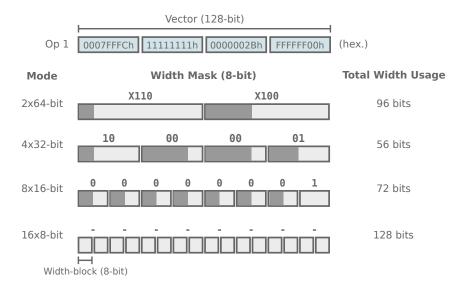

| 4.1  | Examples of the widths detected with different width-block sizes                    | 38       |

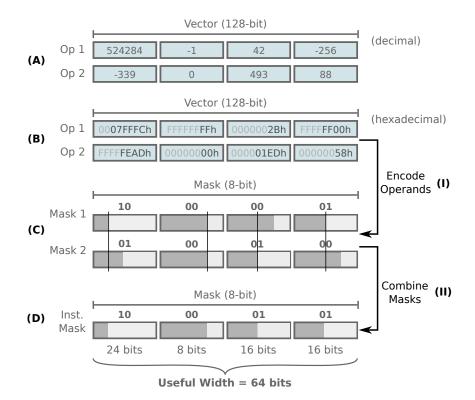

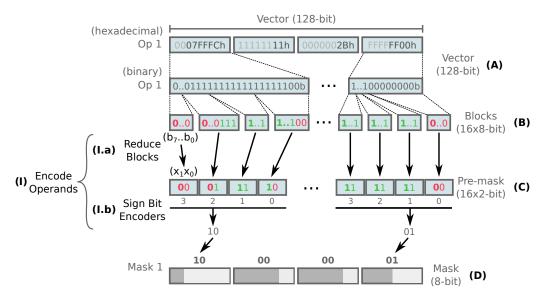

| 4.2  | Width encoding example                                                              | 39       |

| 4.3  | Details of the width encoding procedure of an operand                               | 40       |

| 4.4  | Width masks examples for different vector modes                                     | 41       |

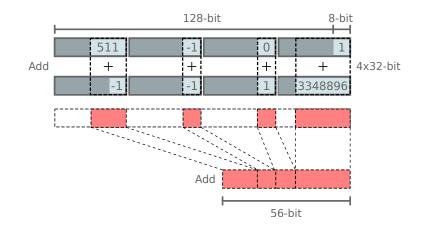

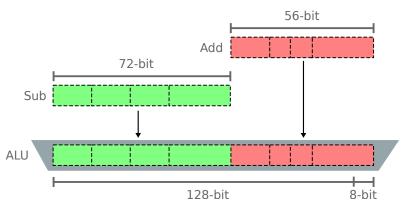

| 4.5  | Vector operand packing in a SIMD Add                                                | 43       |

| 4.6  | Implementation of a irregular element size vectorized adder unit                    | 44       |

| Selection of partial products for an irregular element size multiplication             | 45                                   |

|----------------------------------------------------------------------------------------|--------------------------------------|

| Fusing two similar vector operations                                                   | 46                                   |

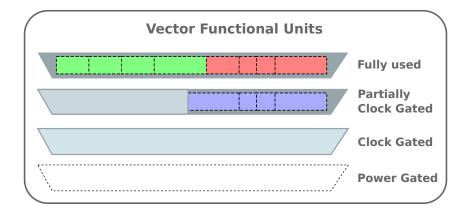

| Example of opportunities for clock and power gating vector functional units            | 47                                   |

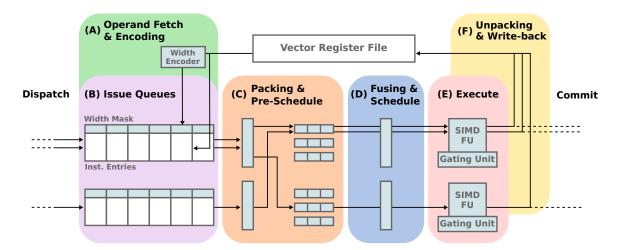

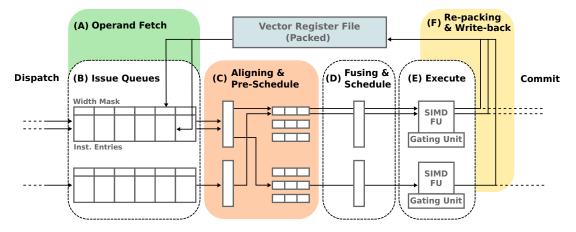

| Detailed changes proposed in the out-of-order execution engine                         | 48                                   |

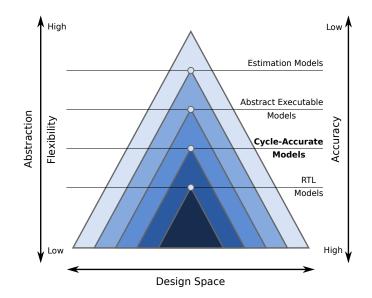

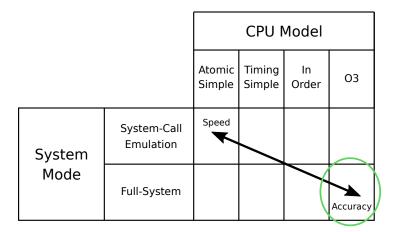

| Comparison of different processor specification and modelling levels                   | 52                                   |

| Comparison of gem5 simulation modes and models                                         | 53                                   |

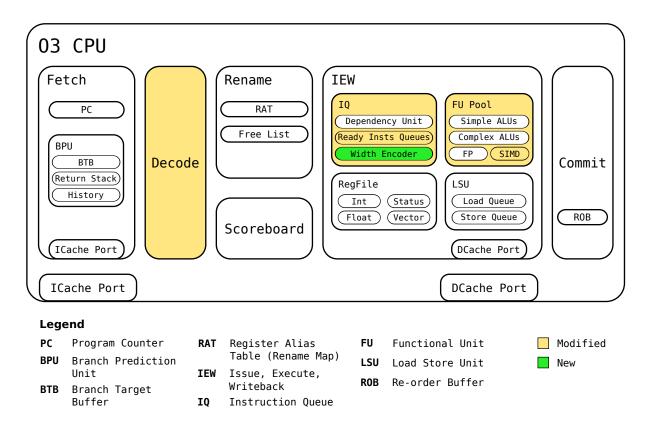

| Modifications made to the internal structure of gem5's O3 CPU model                    | 56                                   |

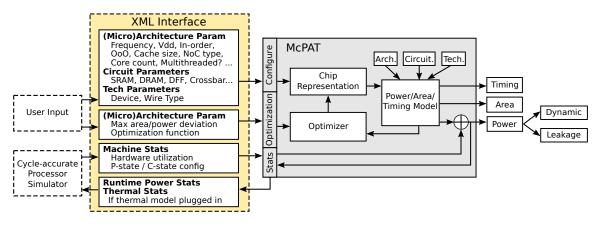

| Block diagram of the McPAT framework                                                   | 60                                   |

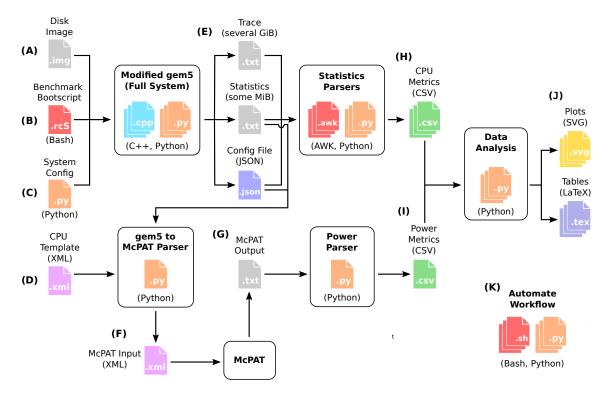

| Description of the experimental workflow                                               | 62                                   |

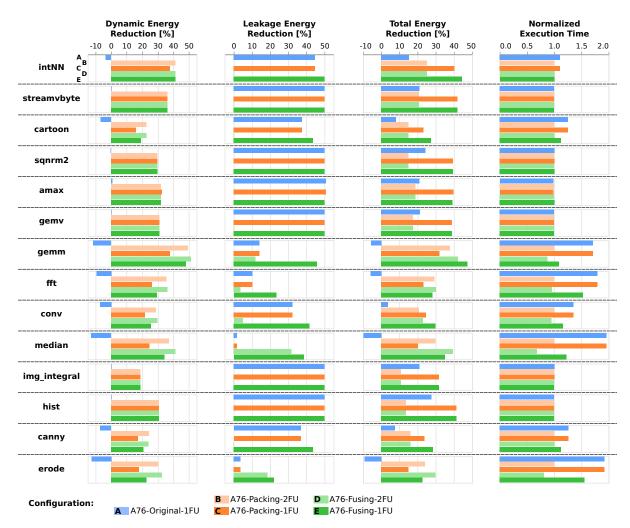

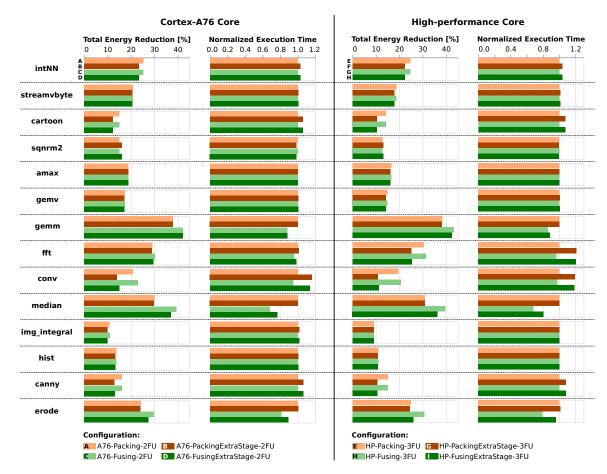

| Energy reduction and normalized execution time with the Cortex-A76 core                | 68                                   |

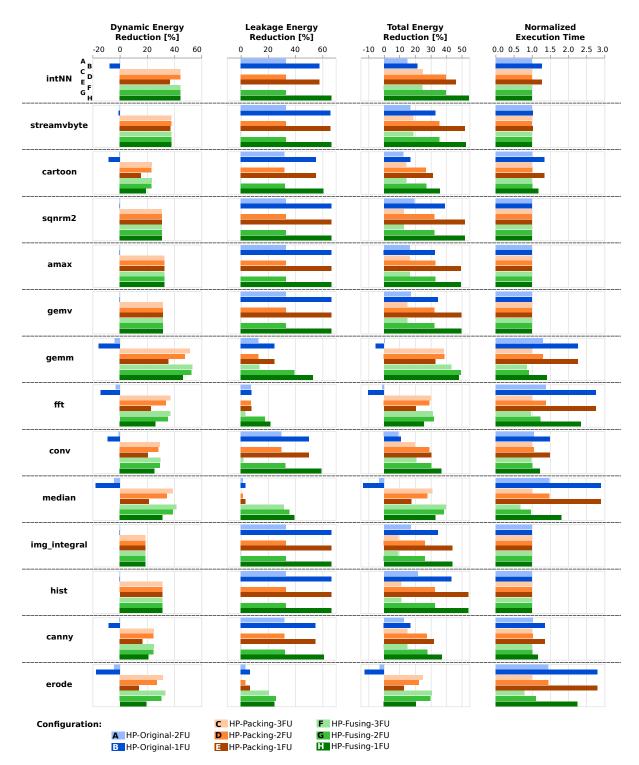

| Energy reduction and normalized execution time with the High-performance core          | 69                                   |

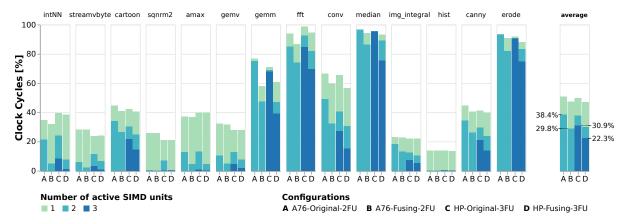

| Active rate of the SIMD units                                                          | 71                                   |

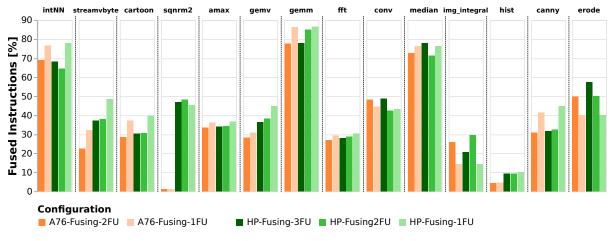

| Percentage of issued instructions that are fused                                       | 72                                   |

| Impact of adding a new pipeline stage                                                  | 73                                   |

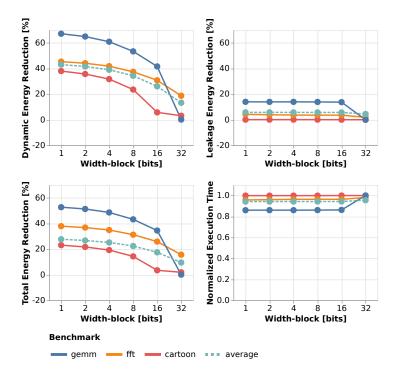

| Comparison of energy savings with different width-block sizes                          | 75                                   |

| Possible extension to the proposed architecture                                        | 78                                   |

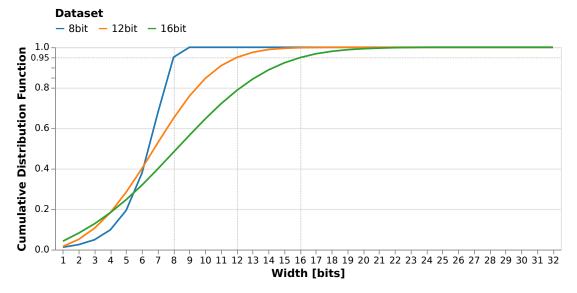

| Cumulative distribution function of the bit-width of the values in the random datasets | 87                                   |

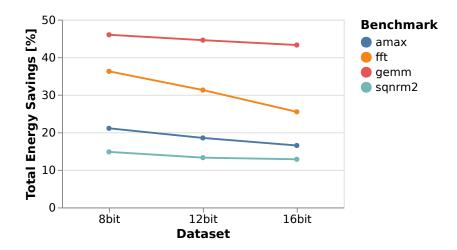

| Energy savings for different datasets                                                  | 87                                   |

|                                                                                        | Fusing two similar vector operations |

# **List of Tables**

| 1.1 | Number and width of integer SIMD units in recent out-of-order processors | 2  |

|-----|--------------------------------------------------------------------------|----|

| 3.1 | Complete list of profiled benchmarks                                     | 31 |

| 4.1 | Width-mask size trade-off                                                | 42 |

| 5.1 | Baseline parameters of the CPU models                                    | 54 |

| 6.1 | Considered simulation modes                                              | 65 |

| 6.2 | Selected benchmarks for this evaluation                                  | 65 |

| 6.3 | Best energy savings Cortex-A76 core                                      | 74 |

| 6.4 | Best energy savings High-performance core                                | 74 |

| A.1 | Sample values from each dataset                                          | 87 |

| B.1 | List of ARMv8 NEON vector instructions                                   | 88 |

# Acronyms

| ALU  | Arithmetic Logic Unit              |

|------|------------------------------------|

| CDB  | Common Data Bus                    |

| CLA  | Carry-Lookahead Adder              |

| CPU  | Central Processing Unit            |

| DSP  | Digital Signal Processor           |

| FP   | Floating-Point                     |

| FU   | Functional Unit                    |

| GPP  | General Purpose Processor          |

| GPU  | Graphics Processing Unit           |

| HPC  | High-Performance Computing         |

| ILP  | Instruction-Level Parallelism      |

| IPC  | Instructions Per Cycle             |

| ISA  | Instruction Set Architecture       |

| MAC  | Multiply-Accumulator               |

| MIMD | Multiple Instruction Multiple Data |

| RAT  | Register Alias Table               |

| RISC | Reduced Instruction Set Computing  |

| ROB  | Re-Order Buffer                    |

| ROI  | Region Of Interest                 |

- RTL Register-Transfer Logic

- SIMD Single Instruction Multiple Data

- SMT Simultaneous Multi-Threading

- WAR Write After Read

- WAW Write After Write

# 1

## Introduction

# Contents 1.1 Motivation 1 1.2 Objectives 3 1.3 Thesis contributions 3 1.4 Thesis outline 4

#### 1.1 Motivation

The increasing number of transistors that implement today's microprocessors has not been accompanied by a corresponding increase in the power efficiency of each transistor, in what is known as the failing of Dennard scaling [1,2]. As a result, power consumption has been the most limiting factor to increase the microprocessors' performance, as a result of the difficulty to dissipate the energy and fully utilize the chip at its maximum clock rate, without compromising its integrity. This power dissipation wall has been imposing a stagnation in the offered computer performance, leading to the need for a computer design shift towards power efficiency [3–6].

General Purpose Processors (GPPs), which will be the focus of this work, have been increasingly used for High-Performance Computing (HPC), such as multimedia, scientific, and engineering applications [6, 7]. Successive architectures in this segment have evolved to match the increased computing power demand by adopting an out-of-order architecture and by having wider issue widths, larger register files, and more functional units. A particular trend in modern Instruction Set Architectures (ISAs) is to include Single Instruction Multiple Data (SIMD) vector extensions [6–9], which allow the execution of the same operation over a vector of several data values in parallel. These instructions provide considerable speed-ups in workloads with data-level parallelism, which are common in HPC. As these SIMD extensions have evolved to adapt to a broader range of applications, the supported vector width has increased to enable higher performance benefits. The recent trend has been to double the vector register size every four years [7–9]. For example, the successive Intel x86 vector extensions have gone from 64-bit vectors (MMX), to 128-bit (SSE) and 256-bit (AVX), to more recently 512-bit (AVX-512) [7, 10]. The ARM SVE extension is already designed to scale up to 2048 bits [9].

However, all these architectural features put an even higher strain on these chip's power limitations. In particular, the execution engine has become an increasingly important power drain in the processor cores, mainly due to the leakage power in its functional units [11, 12]. Moreover, as SIMD extensions became increasingly relevant in high performance and their vector length increased, several and wider integer vector units have been included per core, as presented in Table 1.1. Hence, these units have become a very significant source in power dissipation in processor cores, so they are a particularly relevant candidate for further improvements in power efficiency.

| Table 1.1: Number | and width of intege | r SIMD units in recen | t out-of-order processors |

|-------------------|---------------------|-----------------------|---------------------------|

|                   |                     |                       |                           |

| Microarchitecture                    | Domain          | ISA (vector extensions) | Integer SIMD Units                                      |

|--------------------------------------|-----------------|-------------------------|---------------------------------------------------------|

| ARM Cortex-A76/A77/A78               | Mobile          | ARM (NEON)              | 2 × 128-bit                                             |

| Samsung Exynos M3/M4                 | Mobile          | ARM (NEON)              | 3 	imes 128-bit                                         |

| Apple A12 (Vortex) / A13 (Lightning) | Mobile          | ARM (NEON)              | 3 	imes 128-bit                                         |

| ARM Cortex-X1                        | Mobile          | ARM (NEON)              | 4 	imes 128-bit                                         |

| ARM Neoverse N1                      | Server          | ARM (NEON)              | $2 \times 128$ -bit                                     |

| AMD Zen/Zen+                         | Desktop, Server | x86 (SSE, AVX)          | 4 	imes 128-bit                                         |

| AMD Zen2                             | Desktop, Server | x86 (SSE, AVX)          | 4 	imes 256-bit                                         |

| Intel Sunny Cove                     | Desktop, Server | x86 (SSE, AVX, AVX-512) | $2 \times 256$ -bit, and<br>1 $\times$ 512-bit (Server) |

In this thesis, a still unexplored opportunity for reducing the power dissipation in SIMD units when handling integer computations is identified and evaluated. The conducted research arose from the observation that most integer computations do not require the whole word width, as their operands can be encoded with a lower number of bits, and can be executed using only a portion of the functional unit's width. In previous literature [13–16], these computations have been denoted as narrow-width, but only scalar instructions were exploited.

However, although vector extensions usually provide instructions to support several element data sizes, these instructions pose the constraint that all elements in a vector must have the same bit-width. Even though most integer element values can be represented using narrow data types (i.e. 8 or 16 bits), the occurrence of a small portion of wider values makes it necessary for the application programmer to use a larger element size, to avoid overflow. Hence, for a large portion of the vector lanes, the bit-resolution of the vector functional units is wasted, which means that a very significant portion of the SIMD unit does not perform any computation.

#### 1.2 Objectives

The main objective of this research is to evaluate the opportunity to exploit narrow-width integer SIMD computations in out-of-order processors and to propose architectural mechanisms to increase power efficiency when handling intensive data-parallel integer workloads.

Achieving this goal first requires collecting and profiling a set of representative applications, which should be not only integer intensive, but also vectorizable, measuring relevant metrics about the width required by the operations and the degree of usage of the SIMD units. These two metrics will show, respectively, the existence and the relevance of this opportunity, and will provide insight on how to design mechanisms to exploit it.

The next step is to propose architectural changes to exploit the narrow-width opportunity, taking into account the characteristics and constraints imposed by out-of-order superscalar processors. The proposed mechanisms should be transparent to the compiler (alleviating the need for code recompilation and toolchain changes) and ISA agnostic (to be adaptable to different architectures and vector lengths). This design step must take into account the compromise between the expected power efficiency gains and the complexity and penalty of implementing the proposed mechanisms in hardware.

Afterwards, the proposed mechanisms should be evaluated using a state-of-the-art architectural simulation tool, making the necessary modifications to implement these architectural changes. Then, a relevant set of metrics to evaluate the impact in the processor operation should be identified and generated by the simulation. Finally, these metrics should be used to estimate the resulting impact in terms of performance and energy consumption, using an adequate power model.

#### 1.3 Thesis contributions

The main novelty presented in this thesis consists in a viable exploitation of narrow-width in SIMD integer operations. This contrasts with other previous authors' works, who identified this narrow-width opportunity, but focused only on scalar instructions. On the other hand, the SIMD execution unit provides particular challenges for optimization, as the overhead of detecting the required bit-width for each vector element is multiplied by the number of elements. Moreover, the proposed scheme must be designed to handle the multiple element modes that vector extensions usually support (e.g. 64, 32, 16, or 8-bit elements). In accordance, the main contributions of this thesis are:

- The identification of a novel opportunity for reducing the SIMD unit power consumption, by exploiting narrow-width vector computations, and an evaluation of its relevance in a variety of applications;

- The proposal of low-overhead mechanisms for dynamic detection of the required operands' width for each SIMD lane (width encoding);

- A new scheme (operand packing) to efficiently pack integer vector operands, by discarding unnecessary sign bits between elements these packed vectors can execute directly in an available portion of existing SIMD units (with minor changes);

- A new mechanism (operation fusing) to agglomerate multiple packed vector instructions for simultaneous execution in a single functional unit;

- A set of architectural modifications to the out-of-order vector execution pipeline of a modern processor to support the proposed packing and fusing mechanisms, as well as to provide the means for a more aggressive application of power and clock gating;

- An implementation of these modifications in the gem5 simulator, using the ARMv8 ISA and its NEON advanced vector extension as a proof of concept, and with processor models based on the ARM Cortex-A76 core;

- An estimation of the impact that the proposed architectural changes have in the energy consumption of the SIMD unit and in its execution time, by adding relevant performance counters and using the McPAT power modelling framework.

#### **1.4 Thesis outline**

Figure 1.1: Outline of the thesis work, with the corresponding steps in the evaluation of the narrow-width opportunity in SIMD.

Chapter 2 starts by introducing the computer architecture concepts and the processor research background that are necessary to understand the work that is developed in this thesis. Then, the previous research works that exploited the narrow-width opportunity in the scalar integer pipeline are also reviewed. As depicted in Figure 1.1, Chapters 3 to 6 follow the typical steps in the evaluation of a new architectural mechanism. Chapter 3 presents a preliminary evaluation of the narrow-width opportunity in SIMD operations, using a modified model of the ARM Cortex-A76 processor core, which shows there are very relevant energy efficiency gains to be exploited. Then, Chapter 4 proposes architectural mechanisms to exploit this opportunity, taking into account the typical design constraints in an out-of-order processor but without tieing these mechanisms to a specific architecture or implementation. Chapter 5 specifies the prototyping architecture and core models, and details how the proposed changes were implemented in a state-of-the-art processor simulator. This chapter also presents the power models used to evaluate the impact of the proposed architectural changes. Finally, Chapter 6 starts by listing the configurations and applications that were considered in the evaluation and discusses and analyses the main results that were obtained. Lastly, Chapter 7 addresses the main conclusions and outlines possible future work opportunities.

2

## **Background and Related Work**

#### Contents

| 2.1 | Contemporary GPP architectures             | 7 |

|-----|--------------------------------------------|---|

| 2.2 | Power efficiency in computer architectures | ) |

| 2.3 | Scalable width datapaths                   | 5 |

| 2.4 | Summary                                    | 1 |

The main architectural features of general-purpose computer architectures are first briefly reviewed, with a particular focus on the superscalar and out-of-order architectures and on the Single Instruction Multiple Data (SIMD) vector extensions. This background is crucial to set the constraints and opportunities for new architectural mechanisms. The prevailing techniques and mechanisms for power efficiency are also introduced, with a particular focus on how to reduce the power dissipation of the execution unit.

Then, the previous approaches for taking advantage of narrow-width integer operations are reviewed. This opportunity is first clearly identified, and the two different approaches to explore it are presented: statically (at compile time) and dynamically (at run-time). After identifying the dynamic approach as the most promising alternative, the most relevant architectural mechanisms proposed in the literature are also described. This review includes the existing work on optimizing the datapath structures, with a particular focus on the execution unit, namely the research on the implementation of addition and multiplication units with variable width.

#### 2.1 Contemporary GPP architectures

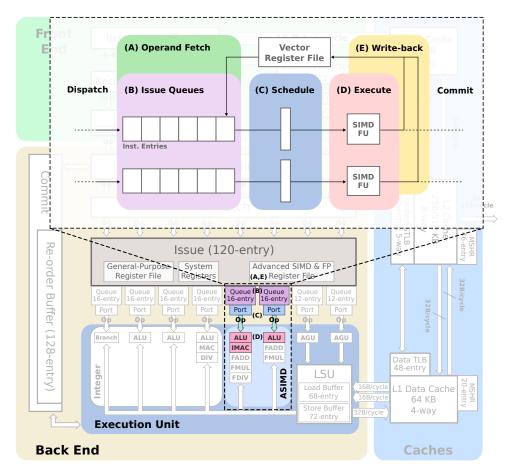

Over the past 20 years, most General Purpose Processors (GPPs) have adhered to the superscalar and out-of-order architecture paradigms [17–19]. These processors take advantage of the Instruction-Level Parallelism (ILP) existing in programs, where several instructions can be executed at the same time, to extract higher levels of performance. Figure 2.1 depicts the microarchitecture of a modern superscalar out-of-order core, the Arm Cortex-A76 launched in 2018, and is used to illustrate the computer architecture concepts and structures which are introduced in this section. This representative microarchitecture will be also used as an example for prototyping the work developed in the following chapters.

Figure 2.1: Microarchitecture of the Arm Cortex-A76, a modern 4-wide superscalar out-of-order core (based on the figure from https://en.wikichip.org/wiki/arm\_holdings/microarchitectures/cortex-a76). Every cycle, this microprocessor can fetch and decode up to four new instructions, and can dispatch up to eight operations to the eight available pipelines, each with its independent issue queue.

A superscalar processor tries to fetch and dispatch several instructions in the same clock cycle and has multiple and different functional units to execute several instructions in parallel (see Fig. 2.1), as long as the original program dependencies are respected. Superscalar execution is usually complemented by out-of-order instruction scheduling, where instructions can be executed in a different order than the original program. Instructions fetched later are allowed to execute first, as long as all their dependencies with previous instructions have already been solved.

However, when instructions are executed out-of-order, the completion of a more recent instruction may overwrite a register operand that is still required by older instructions. Futhermore, if two instructions write to the same register in the wrong order, the final value in that register is incorrect. These two data hazards, denoted as Write After Read (WAR) and Write After Write (WAW), respectively, are usually solved by another mechanism typically associated with these processors: register renaming. Register renaming solves the reuse of the same architectural register, which is not an actual dependency, by allocating a new physical register to store the new value. The correspondence between the architectural registers (in the code) and the physical registers (in the hardware) is abstracted by using an intermediate table of pointers, which is usually called Register Alias Table (RAT) or rename map. Hence, a new rename stage is added after the instructions are decoded and before they are dispatched to an issue queue (see Fig. 2.1), which allocates a new register for the result and updates the corresponding pointer in the RAT.

However, the occurrence of branch instructions greatly limits the possibility of exploiting ILP, since which instructions should be executed after depends on the result of the branch condition. This control dependency is solved by predicting the result of the branch and fetching instructions accordingly. The superscalar out-of-order scheme is therefore complemented with speculative execution, where instructions resulting from branch prediction are allowed to execute but not to commit their results immediately, that is, to change any permanent state of the processor. This way, in the event of the prediction failing, the correct execution state can be recovered by deleting the instructions waiting to commit, without leaving any lingering effect. An auxiliary structure keeps track of the original instruction issue order, the Re-Order Buffer (ROB), so that the instructions are committed in order and only when they are no longer speculative.

These techniques allow for an increased performance, as the processor can maintain a higher instruction throughput and can more easily hide the latency of more time-consuming instructions (e.g. floating-point, SIMD and memory operations). However, this is traded for increased complexity in the processor control structures, as it must be able to fetch, decode, rename, execute, and commit several instructions at the same time, verifying and handling all the dependencies between them. A classical approach to handle all this complexity is to distribute the control of the instruction scheduling, in a scheme known as the Tomasulo's algorithm [17]. This approach relies on dispatching the decoded instructions to one of the multiple issue queues available (also called reservation stations), each associated to a cluster of functional units (execution ports), depending on the instruction type (see Fig. 2.1). Each issue queue is responsible for monitoring when its instructions are ready for execution, by scanning the Common Data Bus (CDB) (shared with the other queues) for the needed operands and buffering them when they are produced. In each clock cycle, it selects as many ready instructions as possible and schedules them for execution, limited by the available functional unit resources.

To sum up, a modern superscalar speculative processor executes instructions out-of-order to exploit ILP, but has to operate in-order in the first pipeline stages (fetch, decode, rename, and dispatch) and in the commit step, so that an application is correctly executed. By following the usual terminology, the front-end is the part of the processor core responsible for fetching and decoding new instructions, and the back-end (or execution engine) is where these instructions are executed.

However, the amount of ILP that can be exploited is often limited [20]. As a result, and to better use the available resources, several modern processors also exploit another form of parallelism: multithreading. In multithreading, different threads that share the same process addressing space are executed concurrently, i.e. without the need for any process context switch. By using the register renaming and dynamic scheduling capabilities of a superscalar processor, instructions from different threads can be executed simultaneously (in the same core) in an approach called Simultaneous Multi-Threading (SMT) [21].

#### SIMD extensions

Another form of parallelism that can be exploited for increased performance is data-level parallelism, where the same operation is performed over several data elements in parallel, following the Single Instruction Multiple Data (SIMD) execution model (see Fig. 2.2). This type of parallelism was first exploited in graphics and multimedia applications, often supported in domain-specific architectures, Digital Signal Processors (DSPs), stream processors, and Graphics Processing Units (GPUs) [22]. However, SIMD architectures have since found application in other broader domains, such as scientific and engineering computing, and machine learning [6,9].

Figure 2.2: SIMD execution model [6].

As the relevance of these application domains increased, new instructions were gradually added to GPPs following the SIMD model, in what is usually called a vector extension in the Instruction Set Architecture (ISA). These SIMD instructions allow for the efficient manipulation (in parallel) of vectors of several data elements, reducing the number of instructions needed to process the input data. Initially, these instructions used the regular 64-bit registers and functional units, packing together several small width values, such as 8-bit and 16-bit [13], but eventually brought the appearance of dedicated vector registers and functional units, with larger widths. For example, the ARM Cortex-A76 microarchitecture, presented in Figure 2.1, includes a dedicated vector register file and two vector execution pipelines, which are shared with the Floating-Point (FP) operations. Since its version 7, the ARM ISA includes an Advanced SIMD extension, which has dedicated vector registers with 128-bit (in version 8), and whose implementation in ARM cores is called NEON (see Section 5.2 for more details).

The current trend is to increase the vector length with each new ISA generation to extract higher performance gains [7, 10]. This trend is exemplified by successive Intel architectures, where the MMX vector extension (1997) started by sharing the scalar 64-bit registers, and the SSE extension (1999) introduced dedicated 128-bit vectors registers, which were increased to 256-bit in AVX (2008) and then to 512-bit in AVX-512 (2013). ARM has taken a step further by introducing SVE, a SIMD extension that can scale to a vector length of up to 2048 bits [9]. As the vector registers increased in size, the datapath resources that are necessary to perform the vector operations have increased too, namely the SIMD register file and execution units. The drawback is the increase in power dissipation [11].

#### 2.2 Power efficiency in computer architectures

The mechanisms presented in Section 2.1 have allowed new levels of performance to be attained but required a corresponding scaling of the available architectural resources. More functional units of each instruction type were added, the decode and commit stages were widened to support a larger instruction bandwidth, and the issue queues and ROBs sizes were increased (see the example microarchitecture in Fig. 2.1). The cost of these structures is paid in increased chip area and power dissipation [12, 18].

For many years, this performance scaling was supported by a steady advance in transistor integration technology, which was maintained at constant power density regimes. However, the reduction in transistor size that allowed for tighter integration had to be accompanied by a proportional reduction in their power dissipation through a downscaling in voltage and current. This is known as Dennard scaling and was valid for 30 years [23,24]. Nevertheless, this scaling has broken down in the past two decades, as a consequence of the increasing sub-threshold leakage current in the transistors, and because their threshold voltage turns further reductions in the supply voltage unfeasible [1,2]. These factors have been fixing the power per transistor, even when their dimensions are further reduced. As a consequence, the overall power consumption by chip area has been steadily scaling upwards with each microprocessor generation. At the same time, the power that can be dissipated by the chip without compromising its integrity is limited, originating a "Power Wall" that limits performance increases. Hence, power consumption became one of the major constraints in computer design, and architectural research has shifted towards power efficiency [3–5], which continues to be a focus in present-day research in all computing domains, from mobile to High-Performance Computing (HPC) [25–28].

Although superscalar processors provide enough architectural resources to sustain a high execution throughput (e.g. several functional units for each operation type and large physical register files), these resources are highly underused during large portions of the execution, namely in code regions with low ILP [29]. A research trend for increasing power efficiency is to implement mechanisms to turn off unneeded resources and cut their power waste [3,5,28,30,31]. A particular focus is given in the literature to optimizing the usage of functional execution units, as they represent a very significant fraction of the energy consumption [11,12,29,32–34]. Some of the most prevailing approaches will be briefly reviewed in the following subsections.

#### 2.2.1 Prevailing techniques for power efficiency

The two principal sources of the microprocessor power consumption are dynamic power and leakage power [3, 30]. Dynamic power is caused by the charging and discharging of the transistors' capacitive load, when switching between states. In the CMOS technology, the dynamic power consumption of a logic block is a function of its activity, as a logic gate only dissipates dynamic power when it switches. This power component is approximated by

$$P_{dynamic} \simeq \alpha C V_{DD}^2 f, \tag{2.1}$$

where *C* is the equivalent capacitance of the load circuit,  $V_{DD}$  is the supply voltage, and *f* is the operating frequency.  $\alpha$  is the activity factor, which varies between 0 and 1, and it is the average fraction of gates switching each cycle.

A significant portion of the dynamic power dissipation is caused by the clock signal tree, which switches at a high frequency and drives a high load. Hence, a common approach for reducing the dynamic power is to turn off the clock signal for unneeded logic blocks [3, 5, 30, 31]. This technique is called **clock gating** and is implemented by partitioning the clock network and by adding enable signals to toggle each portion.

The other main component of power dissipation is leakage (or static) power, which is caused by the transistors' leakage currents, which dissipate power even when the gate is not switching [3]. It is composed of two main components: sub-threshold leakage, which is due to weak inversion currents

across the device; and gate leakage, which is caused by tunnelling currents through the gate oxide. Hence, leakage power is given by

$$P_{leakage} = V_{DD}I_{leak} = V_{DD}(I_{sub} + I_{ox}),$$

(2.2)

where  $V_{DD}$  is the supply voltage,  $I_{sub}$  the sub-threshold leakage current, and  $I_{ox}$  is the gate leakage current. Due to the shrinking in transistor size and the consequent increase in leakage current, leakage power has become extremely relevant and is a major concern in microprocessor design [4,32].

A common technique for reducing leakage is **power gating**, where the power supply for the idle logic blocks is cut off [32, 35–38]. Power gating suppresses both dynamic and leakage power consumption in that block, but has the drawback that it requires long wake-up delays when restoring the supply voltage, and has a significant energy overhead in the state transitions. Hence, its usage only outweighs the cost when the gated block is idle for an extended period. Power gating is implemented by placing a header transistor between the supply voltage and the supply of the circuit portion to be power gated, which is controlled by a sleep signal. As clock and power gating have different trade-offs, it can be advantageous to add support for both techniques in the microprocessor's components and to trigger them concurrently [36].

Another widely used power management technique is **dynamic voltage and frequency scaling**, which is similar to power gating in the sense that either the supply voltage is lowered to reduce leakage currents, or the frequency is lowered to reduce the switching rate. However, instead of completely cutting the supply voltage or the switching currents, they are simply reduced gradually [30, 35]. Hence, the targeted circuit block can still operate normally, and the decreased voltage/frequency results in a consequent reduction of dynamic and leakage power (see Equations 2.1 and 2.2). However, as reducing the supply voltage increases gate delays, the frequency must also be lowered for the circuit to function properly. Hence, varying the voltage and frequency during execution allows different trade-offs between power saving and performance reduction.

#### 2.2.2 Power gating unused functional units

Functional units represent a very significant fraction of the microprocessor power dissipation, particularly in terms of leakage power, and several previous authors have focused on reducing their power dissipation when idle, using power gating [11, 12, 29, 32–34]. The crucial challenge in this approach is deciding when to gate a functional unit. Power gating techniques have a significant latency when waking up a gated unit, which cannot be used immediately [29]. If a functional unit is kept in the sleep mode for too long, it might significantly hinder performance. Moreover, turning off the functional unit has a transition delay: when the supply voltage is decreasing, the power dissipation gradually decreases [32], so the

earlier the power gating is initiated in an idle period, the better (see Fig. 2.4). Finally, the transitions when turning off and on this mechanism have a power overhead, so the idle period must be expected to last long enough to outweigh that cost.

Rele et al. [29] proposed a software-based approach, where the hardware gating mechanisms are controlled by new instructions, which hint on when to turn functional units off or on. The compiler is responsible for identifying regions where each functional unit type has low activity and trigger their sleep mode.

More recent literature focuses instead on dynamic hardware mechanisms, which detect the run-time usage of the functional unit and use predictors to decide on whether to trigger power gating during idle periods [12,32,33]. These authors propose the addition of an architectural structure associated with the functional unit that monitors its activity (idle signal) and uses some control logic to decide on when to generate a sleep signal. When the sleep signal is triggered, a leakage control mechanism power gates the functional unit into a low leakage mode (Figure 2.3).

Figure 2.3: Functional unit's power gating control mechanism [12].

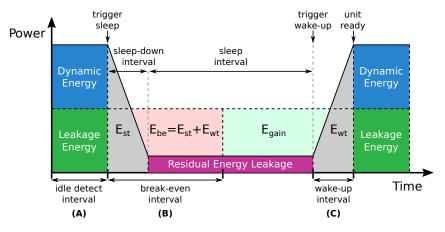

Hu et al. [32] proposed a model to evaluate the potential of power gating an idle functional unit, introducing three main intervals worth considering in a gating mechanism (see Fig. 2.4). The idle detect interval (A) begins when the functional unit becomes idle until the sleep signal is generated; the breakeven interval (B) is the interval of time since the sleep signal is triggered until the leakage energy saved  $(E_{be})$  outweighs the energy overhead in the sleep  $(E_{st})$  and wake-up  $(E_{wt})$  transitions; the wake-up interval (C) corresponds to the period from the moment when the wake-up signal is triggered until the functional until the functional unit is ready for issue.

Hu et al. [32] also proposed a mechanism for generating the sleep signal, consisting on a simple state machine which counts the number of idle cycles and triggers the sleep mode when a certain static threshold is reached. The threshold for each functional unit type is decided at design time, based on their model of the break-even interval and experimental testing. They reach a detection threshold of around 6 to 12 cycles for floating-point units, as a compromise between losing gating opportunities and mispredicting short idle periods. They reported that with the proposed mechanism, the floating-point

**Figure 2.4:** Time-intervals in power gating as described in [32] (also based on the figure in [39]).  $E_{be}$  is the breakeven energy which is required to outweigh the overheads in the sleep transition,  $E_{st}$ , and in the wake-up transition,  $E_{wt}$ . The remaining leakage energy savings correspond to the actual energy gain,  $E_{gain}$ . The power curves in this diagram are simplified.

unit is power gated for up to 28% of the execution cycles, with only a 2% performance loss.

Youssef et al. [12] argued that the accuracy of this counter mechanism could be increased by allowing the sleep threshold to change dynamically, adapting to the currently running application. Their implementation raises the detection threshold when idle periods are frequently interrupted by functional unit usage spikes, and lowers the threshold when the functional unit usage is infrequent and the probability of saving energy when gating is high. They reported that their mechanism improved the accuracy of correctly detecting an idle period from an average of around 40 - 60% to 98%. Lungu et al. [33] argued that even though these mechanisms can provide very relevant leakage power savings (as much as 99%), they can also cause significant increases in power consumption (up to 70%) when there is a systematic misprediction. They proposed improving the sleep control unit by adding a success monitor, which predicts whether a gating opportunity is likely to cause power loss based on previous occurrences, cancelling the sleep signal if that probability is high. They further proposed introducing a maximum power loss threshold which, when exceeded, aborts all sleep opportunities during a specified period.

#### 2.2.3 Reducing the SIMD units power dissipation

SIMD functional units, due to their larger width, represent a significant contribution to power dissipation, namely leakage power, so they are a particularly relevant candidate for applying power efficiency techniques. Kumar et al. [11] tackled this problem in a complementary way to the previously discussed gating mechanisms, focusing on keeping the SIMD units idle for long periods. By increasing the duration of gating intervals and reducing the transitions between the sleep and ready states, the effectiveness of the gating mechanism is improved.

To attain this objective, they propose a mechanism that identifies short duration spikes in the SIMD

functional unit usage, and devectorizes the corresponding instructions, trading a slight performance penalty for more significant power benefits. However, their approach has a significant drawback, as the profiling and devectorization are performed dynamically at run-time, which requires an extra layer between software and hardware, with power and delay penalties.

Another shortcoming is the performance reduction from the devectorization. However, the authors propose an interesting solution for reaching a better compromise between the power dissipation reduction and this performance decrease, by performing partial devectorization. In regions with intermediate SIMD intensity, they propose gating only half of the SIMD unit and dynamically splitting vector operations into two, so that each half of the vector is computed separately. However, this approach increases even more the additional complexity in the dynamic translation between software and hardware.

#### 2.3 Scalable width datapaths

Integer values are typically stored and computed using the processor's default bit-width, which for most modern GPP corresponds to 64 bits. However, most of the computed values are small when compared to the full integer range and can be encoded using only a small portion of those bits. The remaining bits that are not required to encode the value represent a waste of energy, as they are not required for computations or for storing that value. The values or computations that present this reduced width pattern have been labelled as narrow-width in the literature [13]. In particular, optimizing the architecture when handling computations over narrow-width operands is a very relevant opportunity for reducing power consumption in the execution unit.

Brooks and Martosini [13] and some later authors [14, 15] have defined the narrow-width representation of an integer value by removing its redundant sign bits on the left: the leading zero-bits or one-bits. This narrow-width definition is especially relevant and prevalent for integer values, where this reduction in the number of bits is done without losing any precision. The width of an integer value is then defined, in bits, as the index of the least significant sign bit (see Fig. 2.5).

| Decimal | Binary                      | Width  |

|---------|-----------------------------|--------|

| 25      | 6 5 4 3 2 1                 | 6 bits |

| -8      | 1111111 <b>1000</b><br>4321 | 4 bits |

| 0       |                             | 1 bit  |

| -1      | 1111111111                  | 1 bit  |

Figure 2.5: Narrow-width integer representation, where redundant sign bits are removed. The index of the least significant sign bit corresponds to the value's width.

Furthermore, an operation itself can be labelled as narrow when the calculation involves two values

of limited width, hence requiring less logic to evaluate. Previous authors have differed slightly in how they classify an operation's width. Some authors only consider the width of the input operands [13], while others also take into account the resulting value [14, 40]. Although it is straightforward to consider the width of an operation as the largest width among its operands, Brooks et al. [13] note that when computing some addition operations, it may suffice to evaluate the portion corresponding to the narrower operand. If there is no carry from the least significant portion of the operation, the remaining bits of the wider operand can be propagated directly. However, this specific optimization is highly dependent on the operation type and the specific value of the operands.

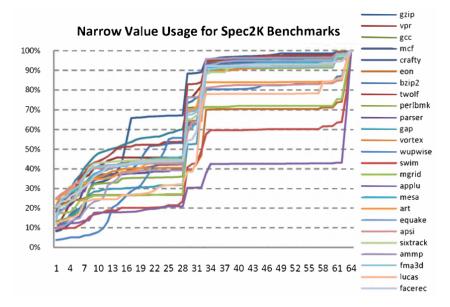

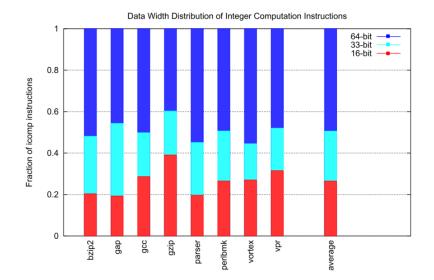

Several authors have evaluated the relevance of exploiting narrow-width operations, using integer intensive or multimedia benchmarks. Based on the SPECint95 benchmarks and a modified SimpleScalar superscalar processor simulation environment, Brooks and Martonosi [13] reported that roughly 50% of the integer instructions had both operands within 16 bits. This ratio increased to a fraction between 80% to 90% for operands within 33 bits. Loh [14] obtained significantly lower fractions, around 30% and 50% for 16-bit and 33-bit, respectively, with the same simulator. They justified the new width distribution with the usage of an updated benchmark (SPEC2000) and because the operation result is also used to calculate the width. Ergin et al. [15] focused on the values stored in the register file, by using a superscalar cycle-accurate simulator based on SimpleScalar and the SPEC 2000 benchmark suite. They found that around 40% of the stored values have 16 bits or less, and 85% are covered by 32 bits. Özsoy et al. [41] obtained similar narrow-width statistics for the SPEC2000 but using the PTLsim simulator, which handles 64-bit x86 instructions. As shown in Figure 2.6, they reported that the 34-bit range covers more than 90% of the values in the profiled applications.

Figure 2.6: Cumulative distribution of narrow-width values occurrence, per benchmark of SPEC2000 [41].

Several authors have also expressed the notion of grouping values in different narrow-width classes, proposing static bit partitions based on their benchmark statistics. Most of the suggested partitions are among three classes (see Fig. 2.7), with 16 bits and 33/34 bits as boundaries [13, 14, 41]. The boundary around 33 bits is attributed to the memory addressing [14], which explains why it is more prone to change with specific benchmarks or even compilers. Grouping into a smaller number of classes introduces a coarser granularity but simplifies the control logic [41].

Figure 2.7: Distribution of integer operations grouped by classes (16-bit, 33-bit, and 64-bit), for several SPEC2000 applications [14].

In some of these analyses, it was also identified that not only narrow-width operations occur frequently, but they also show strong temporal locality. An instruction that recently operated on narrowwidth values has more probability to perform narrow computations again, as it will likely manipulate the same type of input data. Loh [14] first found out that 90% of the instructions have the same width as the last three occurrences of the same instruction type, and 86% for the past seven instances. This temporal locality makes it possible to develop width prediction mechanisms that enable the detection of narrow-width instruction early in the pipeline [14, 15, 41], with low misprediction rates, even before the operands are known, or the result is computed.

Hence, narrow-width values are a highly relevant opportunity for microarchitectural optimizations, as the logic involved in performing calculations and storing these values is simplified. A narrow-width operation can be performed using a narrower Arithmetic Logic Unit (ALU), and its operands and result can be transferred in the datapath using a reduced bus-width and can be stored more compactly in the register file or even in memory.

#### 2.3.1 Software based techniques

A possible approach to exploit narrow-width operands at the microarchitecture level is to explicitly provide the programmer with instructions to more efficiently manipulate smaller resolution operands. SIMD instructions are themselves an example of this, as they can operate on individual elements of up to 8 bits, in most ISAs [9,42,43]. In this case, the instruction itself encodes the operand's width, so the use of narrow-width operands has to be decided on compile-time. The performance efficiency of this approach relies on having architectural structures conveniently adapted to compute and store several values in parallel, but these values must all have the same width.

A different software-based technique was proposed by Canal et al. [44], where the binary instruction explicitly encodes the width required for an integer operation, and its execution is optimized by gating the unneeded datapath portion.

These static solutions have the advantage that the architectural optimizations can be performed with low control overhead, and can be identified very early in the pipeline, as soon as the instructions are decoded. However, these software-based approaches rely on compile-time analysis to estimate the width bounds for each operation, in order to identify which instructions require less resolution. The compiler must perform a conservative estimation, as no overflow should occur due to insufficient resolution, independently of the data input, which results in losing a significant portion of the narrow-width opportunities. In particular, for the SIMD instructions, even if only a small fraction of the elements requires a larger width, all operations have to be performed using this higher resolution.

A possible solution to reduce the number of missed opportunities is to allow the resolution encoded in these instructions to be speculative. This approach relaxes the constraints on the static analysis, which only needs to set the most probable width of the operand and result. Pokam et al. [16] proposed that the instruction encoding should be only a hint to the architecture and that there should be hardware mechanisms to recover from width overflow. If the hinted width is not enough to perform the computation, a replay trap should be set to restart the instruction with a wider datapath resolution.

However, these replay mechanisms come at a high performance and energy cost, as not only is the executed instruction wasted, but this may also interfere with the execution of the other instructions in the pipeline. Moreover, the compiler is still forced to be conservative to some degree in the estimation of the width bounds to keep the under-prediction rate low. Futhermore, the same program region can have different width patterns at different moments of execution, which makes the static analysis even more complicated and may require more complex program binaries.

Moreover, these approaches require making complex changes to the compilers and recompiling the applications to take advantage of the new optimized instructions. This increases the cost of deploying these software-based solutions.

#### 2.3.2 Dynamic hardware-based approaches

As it was referred before, a considerable portion of narrow-width computations can only be detected at run-time, when the actual values are available. The width that is required by each value can be evaluated using leading zero or one-bit detectors. Hence, dynamic mechanisms implemented at the hardware level can better exploit narrow-width computations, for increased performance and power-efficiency, by conveniently scaling the datapath structures during run-time or by better utilizing the already available resources.

Most of the existing work in dynamic narrow-width optimization has been developed in out-of-order superscalar processors [13, 14, 40, 41]. Apart from its higher relevance in the GPP segment, this can be explained by the wider instruction window and higher amount of available datapath resources, which present more opportunities for width related optimizations.

Brooks and Martosini [13] suggested some optimizations to the scalar datapath at the level of the issue queue and the functional unit schedulers. By using leading zero and one detectors, the integer instructions waiting for execution are tagged according to the width of their operands, as soon as they are known (See Figure 2.8). They proposed two different optimization mechanisms when narrow instructions are issued to the corresponding functional unit:

- For power efficiency, they suggested clock-gating the unneeded resolution of the functional unit, when the instruction is issued;

- For performance, they proposed fusing multiple narrow operations of the same type for executing simultaneously, in the same ALU, in a form similar to auto-vectorization.

| Issue Queue          |                           |              |          |  |  |

|----------------------|---------------------------|--------------|----------|--|--|

| Op Source 1 Source 2 |                           | Narrow?      |          |  |  |

| add                  | 000000010001              | 00000000010  | yes      |  |  |

| sub                  | 010100110101              | 011011110101 | no       |  |  |

| add                  | 000001000010 000000010011 |              | yes      |  |  |

|                      |                           |              |          |  |  |

| Functional Unit      |                           |              |          |  |  |

|                      | 000001000010              | 000000010001 | Source 1 |  |  |

| <br>add              | 000000010011              | 000000000010 | Source 2 |  |  |

| A                    |                           |              |          |  |  |

↑ Kill Carry

Figure 2.8: Example of an opportunity to fuse two narrow-width addition operations waiting for execution in the issue queue (adapted from [13])

For the fusing approach, they only consider simpler and more frequent arithmetic operations, such as additions, where the functional unit can be shared by cutting the carry chain and multiplexing the operands to different bit ranges. The performance increase is achieved with the higher execution throughput using the same functional unit resources, as long as enough opportunities for fusing are encountered during the program execution.

They argue that the overhead in terms of circuit area and power consumption for their approaches is not significant, and it is mainly due to the leading bit detectors and width select multiplexers. For the power efficiency method, they estimated a reduction in power consumption of the integer unit of 54.1% for the SPECint95 benchmark suite. For the performance approach, they estimated an average speedup between 4.3% and 6.2%, with the same benchmarks.

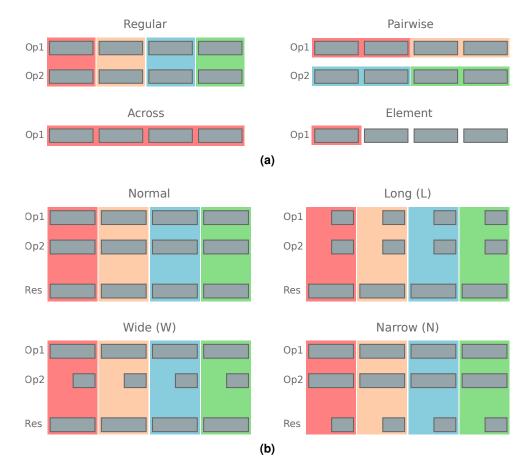

Loh [14] presented a similar approach to increase the superscalar processor performance by fusing several one cycle integer narrow-width operations for execution in the same ALU. However, different operation types can be fused, in his approach, extending this technique from a SIMD to a Multiple Instruction Multiple Data (MIMD) approach. He argued that existing ALU designs that already support SIMD and multimedia extensions only have to be extended to have support for different opcodes for each sub-operation.

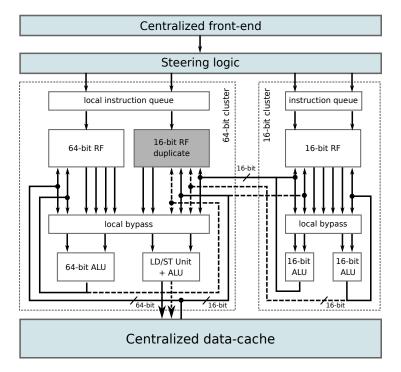

Rochecouste et al. [40] argued that the added complexity to handle instructions of different widths, in particular at the scheduler and in register file accesses, justify partitioning the superscalar microarchitecture into two clusters which process instructions of different width. These full and narrow-width cores have independent register files and datapaths, with the corresponding resolution, as illustrated in Figure 2.9. The narrow core only executes instructions where both the operands and the result are narrow, which they define as 16-bit or less. The narrow register file must be replicated in the full-width core, for the execution of instructions which have both types of operands or result. They argued that there are enough narrow and full instructions interleaved in the execution to keep both cores working at a good rate.

Islam and Stenstrom [45] focused on optimizing narrow-width memory instructions, proposing an additional cache for these narrow values. This narrow-width cache would be placed alongside the L1 data cache and connected directly to the Central Processing Unit (CPU) in parallel. This new cache would also be connected to the higher-level cache hierarchy through a narrow-width detection block, which would detect narrow operands closer to memory and fetch them directly.

#### 2.3.3 Scalable width structures

These narrow-width optimization mechanisms require datapath structures that can adapt their bit-width during run-time, namely at the level of the Functional Units (FUs), register files, or caches. Several implementations of such structures have been proposed in the literature that either turn off part of their resolution when handling narrow-width values or that use their full width to pack several narrow-width values.

Figure 2.9: Cluster partitioned approach for narrow-width exploitation [40]

#### 2.3.3.A Functional units

Several implementations have been proposed for integer FUs capable of supporting operands with multiple widths, mainly developed to provide support for SIMD ISA extensions. These implementations focus on multiplication and addition operations, although it is reasonable to assume that logical and shift operations are easier to implement.

Själander and Larsson-Edefors [46] proposed an integer multiplier design that adapts its bit-width to the operands. Their implementation also allows the multiplier logic to be efficiently shared for computing two narrow-width operations in parallel. They argued that the same could be done for other functional unit types, namely adders.

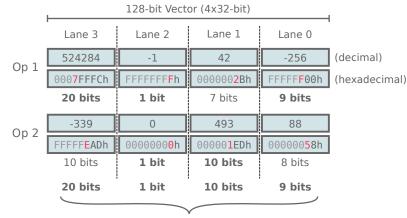

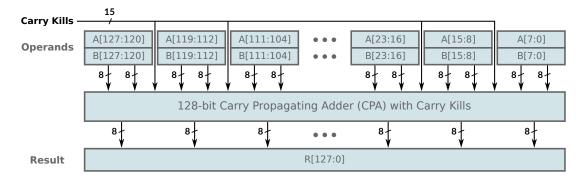

In the context of SIMD functional units, Balakrishnan and Nandy [47] and Karthikeyan and Ranganathan [48] went further and argued that the default element sizes (namely 8-bit, 16-bit, 32-bit, and 64-bit) miss some important media applications, such as medical imaging with 12-bit pixels and 9-bit encoded MPEG files. In accordance, they proposed changes in the SIMD FU for supporting arbitrary element sizes in addition and multiply-add operations, by modifying the carry-lookahead and Wallace tree algorithms, respectively, with a small hardware overhead.

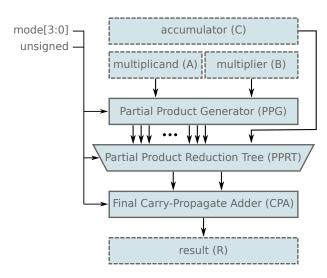

For the efficient implementation of integer multiply and multiply-accumulation SIMD units, Danysh and Tan [49], and Krithivasan and Schulte [50] have proposed designs that allow the same multiplier hardware to be shared for different operation modes. The Multiply-Accumulator (MAC) design proposed

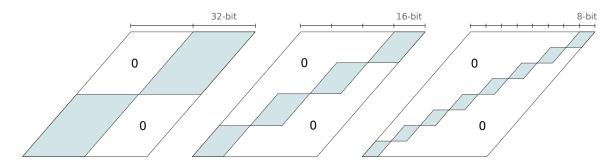

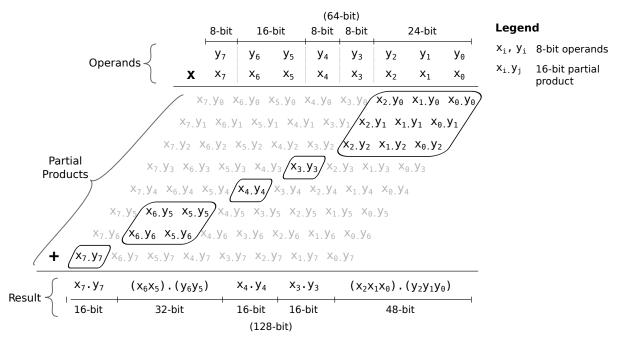

in [49] allows the execution of either one operation with 64-bit operands, two with 32 bits, four with 16 bits, or eight with 8 bits, both signed and unsigned. In both cases, the proposed designs are based on a similar scalar multiplier architecture, which is composed of a partial product generator, a Wallace reduction tree and a final carry-propagate adder (see Figure 2.10). The units are vectorized by selecting only the partial products corresponding to the elements in each mode and by killing the cross-products between boundaries of different elements (zeros in Figure 2.11). By aligning the partial products for each element so that there is no overlap with other elements (see Figure 2.11) the same reduction tree can be used for each mode.

The main difference between these two architectures is the implementation of the partial product generator, which is a Booth encoder in [49] and a matrix multiplier based on Baugh-Wooley technique in [50]. Using a Booth encoder reduces the number of partial products to half and allows for a smaller reduction tree. However, it requires more complex control logic for supporting multiple element sizes, as it requires suppressing carries between element boundaries in the reduction tree and final adder.

More recently, in the context of floating-point MAC architectures that support multiple precisions, several works [51–53] have proposed similar designs for implementing a mantissa multiplier (which is identic to an integer multiplication) that is shared between precision modes.

Figure 2.10: Vectorized MAC design proposed in [49].

#### 2.3.3.B Register file

Large register files also play a fundamental role in sustaining the performance of a superscalar processor and represent a significant portion of dynamic and static power dissipation. Several authors have focused on taking advantage of the lower number of bits required by narrow-width values to use register logic more efficiently, either for increased performance, by compacting narrow values and increasing the

Figure 2.11: Selecting the partial products for 32-bit, 16-bit, and 8-bit operation modes, using the same hardware of a 64-bit scalar MAC unit.

number of free registers available, or for power-efficiency, by turning off unused portions of the register file.

However, register file optimization is quite challenging for a superscalar processor, mainly because of register renaming, as the registers are allocated before the value to be stored is known. To handle this, Ergin et al. [15] proposed conservative and speculative approaches. In the conservative approach, a full-size register is allocated during the renaming phase, and as soon as a narrow result is obtained, the empty space can be reallocated. In the speculative approach, the width of the instruction is predicted before renaming, and a register with an adequate size is allocated. If there is an over-prediction, the extra resolution can be either reallocated or wasted. Under-prediction is more difficult to handle, as it may lead to deadlocks if a suitable register is not found. The recovery mechanism depends on the details of the implementation but may require squashing more recent instructions to free-up registers.

Based on this same idea, two different techniques to optimize narrow-width value storage can be identified in the literature: packing and partitioning. In the packing technique, several narrow values share the same full-size register, and an extra pointer or mask is used to address the sub-registers. Ergin et al. [15] proposed a register packing approach, where four classes of values (16, 32, 48, and 64-bit) are stored in 8 byte physical registers. These values are stored in any of the 8 byte slots, not necessarily contiguously, by using a 4-bits mask to encode where each byte is stored. Each physical register is then addressed by a pointer and this mask. To manage the allocation and reallocation of these sub-registers, they also proposed independent lists of free registers for each class. Similarly to operation fusing, this register packing technique is more focused on performance, as it allows the existing resources to be better used. Although it does not reduce, by itself, the register file power consumption, it can be combined with other approaches, such as turning off unused parts of the register file.

In the register partitioning approach, the physical register file is partitioned in regions of different widths, where the unneeded resolution is either removed or gated, providing different register size classes. Özsoy et al. [41] proposed both a static scheme for this partition, where the number of registers for each class is fixed, and a dynamic scheme, which can change this partition in run-time, by using