### UNIVERSIDADE DE LISBOA INSTITUTO SUPERIOR TÉCNICO

## Energy-Efficient Computing: Adaptive Structures and Data Management

Nuno Filipe Simões Santos Moraes Neves

Supervisor:Doctor Nuno Filipe Valentim RomaCo-Supervisor:Doctor Pedro Filipe Zeferino Aidos Tomás

Thesis approved in public session to obtain the PhD Degree in Electrical and Computer Engineering

Jury final classification: Pass with Distinction

### UNIVERSIDADE DE LISBOA INSTITUTO SUPERIOR TÉCNICO

## Energy-Efficient Computing: Adaptive Structures and Data Management

Nuno Filipe Simões Santos Moraes Neves

Supervisor:Doctor Nuno Filipe Valentim RomaCo-Supervisor:Doctor Pedro Filipe Zeferino Aidos Tomás

Thesis approved in public session to obtain the PhD Degree in Electrical and Computer Engineering

Jury final classification: Pass with Distinction

#### Jury

**Chairperson:** Doctor Isabel Maria Martins Trancoso, Instituto Superior Técnico, Universidade de Lisboa

#### Members of the Committee:

Doctor João Manuel Paiva Cardoso, Faculdade de Engenharia, Universidade do Porto Doctor Horácio Cláudio de Campos Neto, Instituto Superior Técnico, Universidade de Lisboa Doctor Arnaldo Silva Rodrigues de Oliveira, Universidade de Aveiro Doctor Nuno Filipe Valentim Roma, Instituto Superior Técnico, Universidade de Lisboa Doctor Ricardo Miguel Ferreira Martins, Instituto Superior Técnico, Universidade de Lisboa

FUNDING INSTITUTION

Fundação para a Ciência e a Tecnologia (FCT)

#### Acknowledgements

The work presented in this thesis would not be possible without the support of many people and institutions.

Firstly, I would like to thank my Ph.D. supervisors Pedro Tomás and Nuno Roma for the tremendous amount of support they gave to me during all these years. This support does not only cover their invaluable guidance and dedication to the entire work, but also all the personal aspects by teaching me how to become a better researcher and constantly challenging me and pushing me out of my comfort zone. Thank you for your trust, your patience, and all the opportunities you gave (and are still giving) me over all these years.

Furthermore, I would like to thank Fundação para a Ciência e a Tecnologia for the financial support under the Ph.D. grant SFRH/BD/100697/2014, project UID/CEC/50021/2019 and project HAnDLE (ref. PTDC/EEI-HAC/30485/2017). I would also like to thank INESC-ID for hosting me, for providing all the conditions necessary for performing my work in the best way, and for the financial support required for the publications and international conferences.

To all the members of the SiPS group for the solidarity and teamwork, as well as to Ana, Aurélia and Elisabete for the provided administrative support. I would like to thank all my closest colleagues João, Nuno, Paulo, Pedro, Roger, Tiago, and Professor Leonel, for their partnership, collaboration and all the good times throughout the years.

To all the co-authors of my publications and people I had the pleasure to work with, especially to Adrien Mussio, Fabien Gonçalves, Henrique Mendes, Nuno Horta, Ricardo Chaves, and Rui Neves. Thank you for your help, recommendations and provided scientific background.

To all my friends, namely Duarte, Gonçalo, João, Pedro and Sónia for their friendship and support from as far back as I can remember.

To all my family and relatives for the incentive they provided during these five years, especially to my mother, Maria de Lurdes, and my father, José.

To Joana for all the support, patience and comprehension during the most difficult times of this journey, for the friendship and for the unconditional love.

Finally, to all of those whom I do not mention here but that directly or indirectly have contributed and helped me to achieve my goals.

### Abstract

Computing efficiency is often regarded as the most challenging goal to achieve cost-effective exascale computing. While the computing market has driven the research for heterogeneous and specialized many-core architectures, several issues must still be addressed to attain the efficiency goals established by the High-Performance Computing (HPC) community. In particular, the processing performance of current computing systems is often conditioned by power constraints and thermal dissipation, forcing most of the chip area to be dimmed or powered down during long periods of time. This issue limits the achievable computing performance, by making the utilization of the available chip area ineffective. Furthermore, most of the research has been focused on the performance-energy efficiency of new processing infrastructures, with the underlying data communication subsystems relying on conventional multi-level cache structures, to mitigate the data access latencies. However, these structures struggle when the application dataset is very large and does not fit in the cache memory, or in the presence of complex memory access patterns, where data-locality cannot be efficiently exploited. This results in costly contention issues that tend to degrade the data transfer throughput and, in turn, limit the system's achievable performance. To tackle all these issues, this dissertation proposes new adaptive computing mechanisms to cope with the efficiency demands of the next generations of computing systems. The research is initially focused on compile-time memory access pattern analysis and code transformations, to enable data streaming mechanisms in conventional cache-based infrastructures. Such mechanisms allow the exploitation of hybrid data communication schemes, targeting runtime data movement adaptation and memory throughput maximization. The devised mechanisms showed to reduce data transfer overheads with efficient data fetching, reutilization, and management techniques, in turn countering the contention that is usually observed in shared interconnections. The same application analysis principle is also exploited for adaptable processing acceleration, through runtime hardware adaptation. It is explored the viability of using partial reconfiguration to balance the raw performance with the corresponding energy consumption, according to the runtime context. The resulting adaptable processing framework allows for significant performance gains and energy consumption reductions, resulting in increased computing efficiency.

#### Keywords

Computing Efficiency, Compiler-Time Analysis, Data Streaming, Adaptable Data Communication, Reconfigurable Computing

#### Resumo

A eficiência da computação é muitas vezes reconhecida como o objetivo mais desafiante para se alcançar uma capacidade de computação em exa-escala. Para atingir esse objetivo, têm sido desenvolvidas inúmeras arquiteturas multiprocessador heterogéneas, com diversos níveis de especialização. No entanto, existem ainda várias questões que terão de ser convenientemente abordadas para alcançar as metas de eficiência estabelecidas pela comunidade de computação de elevado desempenho. Em particular, o desempenho dos sistemas de computação atuais é condicionado por restrições de energia e dissipação térmica, forçando a maior parte dos recursos do sistema a estarem desligados durante uma parte significativa do tempo. Este problema torna a utilização dos recursos disponibilizados pelo sistema pouco eficiente, limitando, assim, o desempenho computacional que é realmente atingível. Além disso, a maior parte da investigação feita nos últimos anos tem sido principalmente focada em novas infraestruturas de processamento, e no seu desempenho e eficiência energética. Em compensação, os subsistemas de comunicação de dados são geralmente suportados em estruturas de cache convencionais, de forma a mitigar a latência de acesso aos dados. No entanto, estas estruturas continuam a não conseguir lidar com conjuntos de dados com dimensão superior à capacidade da memória cache, nem com padrões complexos de acesso à memória, em que a localidade de dados não é eficientemente explorada. Isto resulta em problemas de contenção que diminuem a taxa de transferência de dados, e, por sua vez, limitam o desempenho do sistema. De modo a abordar estes problemas, esta dissertação propõe novos mecanismos de computação adaptativos para alcançar os níveis de eficiência necessários para as próximas gerações de sistemas de computação. A investigação é inicialmente focada na análise de padrões de acesso à memória em tempo de compilação e em transformações de código, de modo a criar um suporte para a utilização de mecanismos de manipulação de cadeias de dados em infraestruturas de cache convencionais. Os mecanismos desenvolvidos permitem a exploração de esquemas híbridos de comunicação, permitindo uma adaptação ao nível do esquema de transferência de dados em tempo de execução e uma maximização da largura de banda da memória. Os mecanismos propostos mostraram ser capazes de mitigar penalizações associadas à transferência de dados tirando partido de técnicas eficientes de aquisição, reutilização e gestão de dados, contrariando, por sua vez, os problemas de contenção que são normalmente observados em barramentos de comunicação partilhados.

O mesmo princípio de análise de aplicações é também explorado no contexto da aceleração do processamento, através da adaptação da arquitetura em tempo de execução. Para o efeito, é explorada a viabilidade da utilização de mecanismos de reconfiguração parcial para balancear o desempenho do sistema com o seu consumo de energia, de acordo com o contexto de execução. As estruturas de processamento adaptáveis propostas permitem atingir ganhos de desempenho significativos e consequentes reduções de consumo de energia, resultando, assim, numa eficiência de computação elevada.

#### **Palavras-Chave**

Computação Eficiente, Análise em Tempo de Compilação, Manipulação de Cadeias de Dados, Comunicação de Dados Adaptativa, Computação Reconfigurável

### Contents

| 1 | Intro | oductio | on                                                          | 1  |

|---|-------|---------|-------------------------------------------------------------|----|

|   | 1.1   | Motiva  | ation and Objectives                                        | 3  |

|   | 1.2   | Contri  | butions                                                     | 5  |

|   | 1.3   | Outlin  | e                                                           | 7  |

| 2 | Bac   | kgrour  | nd and State-of-the-Art                                     | 9  |

|   | 2.1   | Overv   | iew of Modern Computing Systems                             | 10 |

|   | 2.2   | Data (  | Communication Schemes and Paradigms                         | 13 |

|   |       | 2.2.1   | Compiler Static Analysis and Memory Access Optimization     | 14 |

|   |       | 2.2.2   | Data Prefetching Techniques                                 | 16 |

|   |       | 2.2.3   | Data Streaming Architectures                                | 20 |

|   |       | 2.2.4   | Discussion                                                  | 22 |

|   | 2.3   | Adapt   | ive Computing                                               | 23 |

|   |       | 2.3.1   | Power Supply Management                                     | 24 |

|   |       | 2.3.2   | Dynamically Reconfigurable Systems                          | 24 |

|   |       | 2.3.3   | Dedicated Programming Frameworks and Execution Optimization | 28 |

|   |       | 2.3.4   | Reconfigurable Communication Systems                        | 30 |

|   |       | 2.3.5   | Discussion                                                  | 31 |

|   | 2.4   | Summ    |                                                             | 32 |

| 3 | Data  | a-Patte | rn Analysis and Stream Transformations                      | 33 |

|   | 3.1   | Model   | ing of Complex Data-Patterns                                | 35 |

|   |       | 3.1.1   | Affine Mathematical Model for Data Indexing                 | 37 |

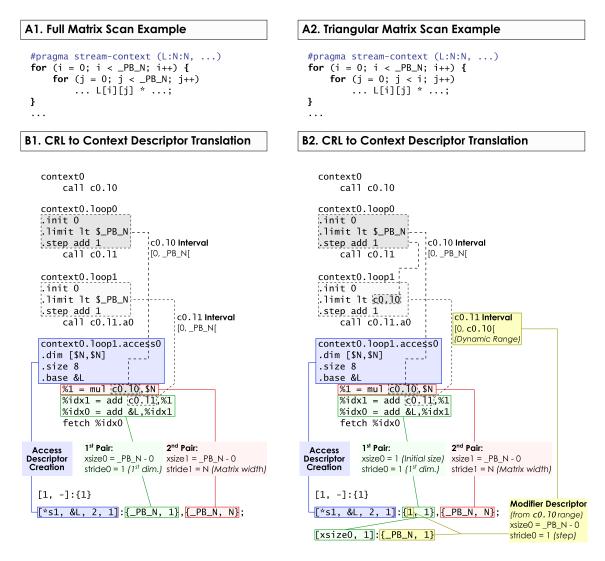

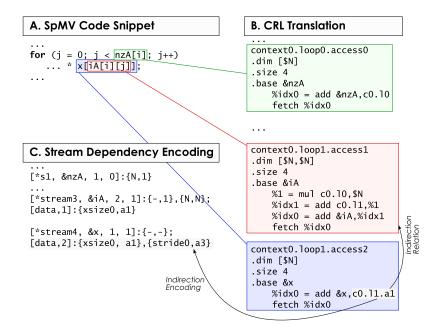

|   |       | 3.1.2   | Memory Access Description Specification                     | 39 |

|   | 3.2   | Comp    | ile-Time Stream Code Generation                             | 42 |

|   |       | 3.2.1   | Compiler Module Overview                                    | 43 |

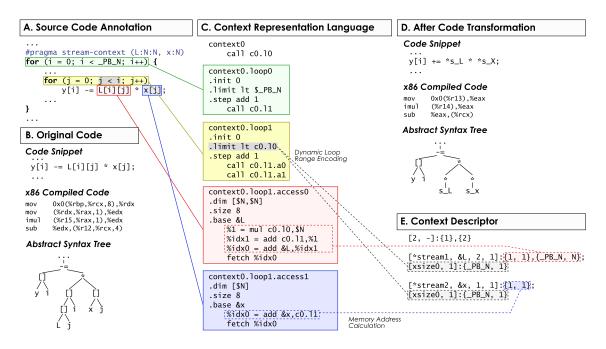

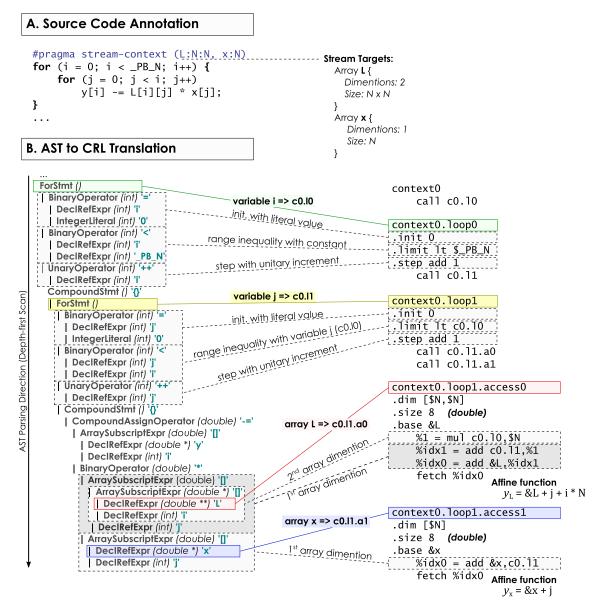

|   |       | 3.2.2   | Context Representation Language                             | 46 |

|   |       | 3.2.3   | Stream Code Generation                                      | 49 |

|   | 3.3   | Prelim  | inary Experimental Evaluation                               | 53 |

|   |       | 3.3.1   | Methodology                                                 | 53 |

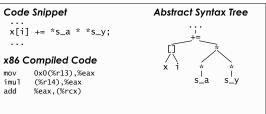

|   |      | 3.3.2   | Data-Pattern Encoding Efficiency                            | 56  |

|---|------|---------|-------------------------------------------------------------|-----|

|   |      | 3.3.3   | Source Code Reduction Evaluation                            | 58  |

|   |      | 3.3.4   | Discussion                                                  | 59  |

|   | 3.4  | Summ    | ary                                                         | 60  |

| 4 | Data | a Strea | m Communication                                             | 61  |

|   | 4.1  | Data S  | Stream Generation                                           | 63  |

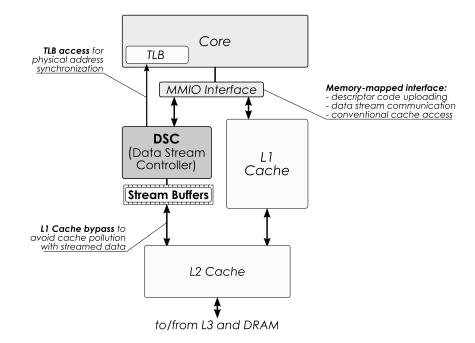

|   |      | 4.1.1   | Data Stream Controller Architecture                         | 63  |

|   |      | 4.1.2   | Streaming Infrastructure Interface and Programming          | 67  |

|   | 4.2  | Data S  | Stream Prefetching                                          | 67  |

|   |      | 4.2.1   | Case Study A: Stream Prefetching on GPGPUs                  | 68  |

|   |      | 4.2.2   | Case Study B: Data Streaming on Modern General-Purpose CPUs | 75  |

|   |      | 4.2.3   | Discussion                                                  | 83  |

|   | 4.3  | In-Cac  | he Stream Communication Paradigm                            | 84  |

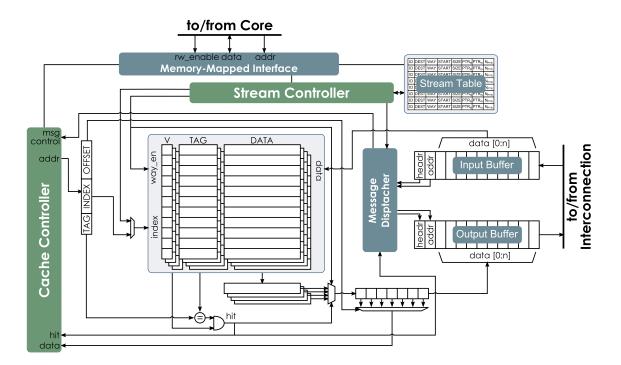

|   |      | 4.3.1   | In-Cache Stream Controller                                  | 85  |

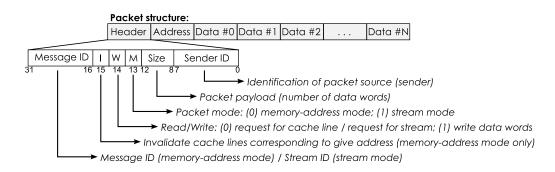

|   |      | 4.3.2   | Communication Infrastructure and Protocol                   | 89  |

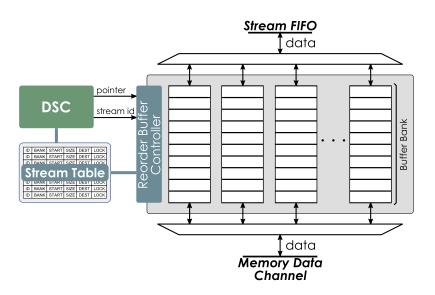

|   |      | 4.3.3   | Memory-Aware Data Stream Generation                         | 91  |

|   | 4.4  | In-Cac  | he Streaming Evaluation                                     | 93  |

|   |      | 4.4.1   | Methodology                                                 | 94  |

|   |      | 4.4.2   | Hardware Resources Overhead                                 | 96  |

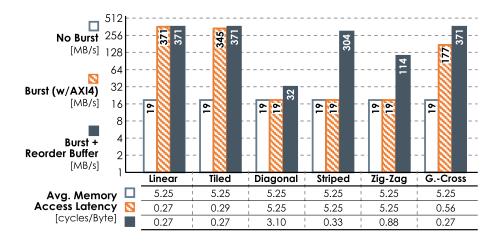

|   |      | 4.4.3   | Stream Generation Efficiency and Main Memory Throughput     | 98  |

|   |      | 4.4.4   | Prototype Evaluation                                        | 99  |

|   | 4.5  | Summ    | ary                                                         | 103 |

| 5 | Ada  | ptive P | Processing Structures                                       | 105 |

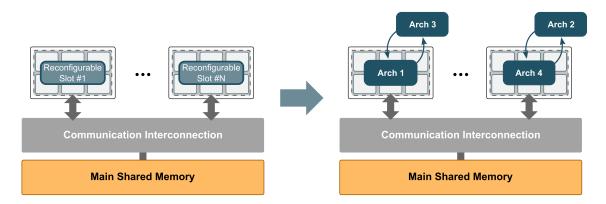

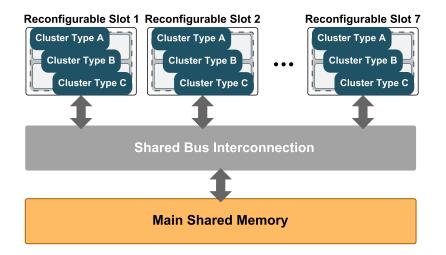

|   | 5.1  | Recon   | figurable Many-Core Accelerator                             | 107 |

|   |      | 5.1.1   | Many-Core Processing Infrastructure                         | 108 |

|   |      | 5.1.2   | Data Access and Interconnection Networks                    | 109 |

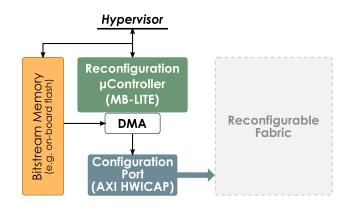

|   |      | 5.1.3   | Hypervisor and Accelerator Management                       | 110 |

|   |      | 5.1.4   | Reconfiguration Engine                                      | 111 |

|   |      | 5.1.5   | Implementation Considerations and Constraints               | 113 |

|   |      | 5.1.6   | Accelerator Configuration and Implementation                | 113 |

|   | 5.2  | Recon   | figuration Management                                       | 116 |

|   |      | 5.2.1   | Runtime Learning and Reconfiguration Policies               | 117 |

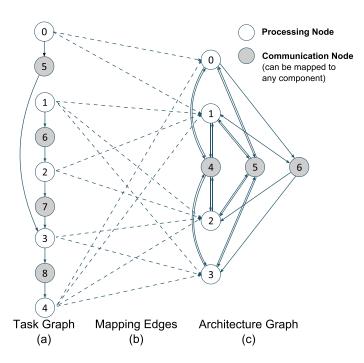

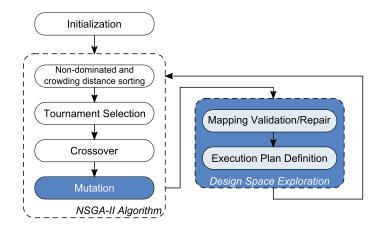

|   |      | 5.2.2   | Compile-time Modeling and Optimization                      | 119 |

|   | 5.3  | Experi  | mental Validation                                           | 129 |

|   |      | 5.3.1   | Methodology                                                 | 129 |

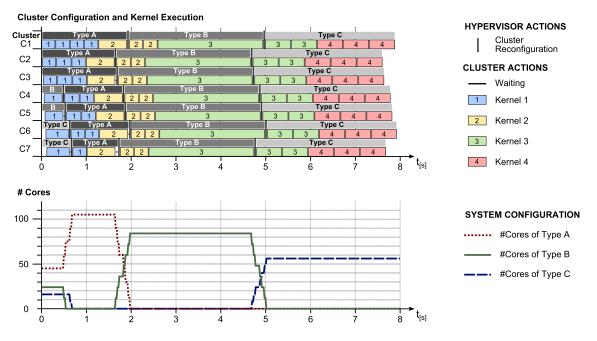

|   |      | 5.3.2   | Case Study A: Learning-based Automatic Reconfiguration      | 131 |

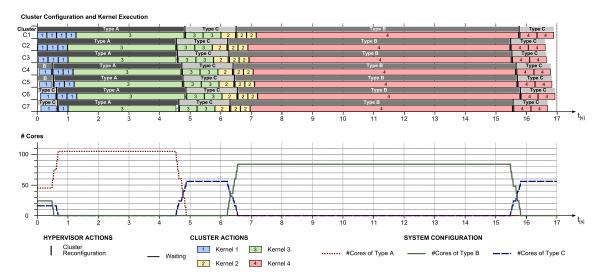

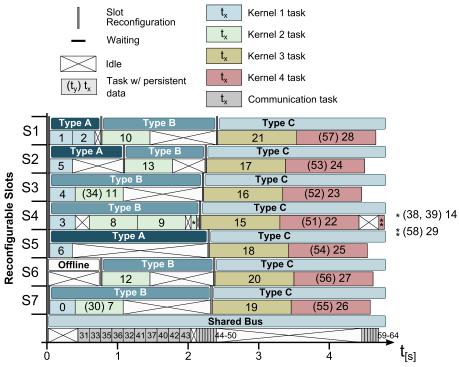

|    |                | 5.3.3  | Case Study B: Compiler-Assisted Reconfiguration         | 135 |

|----|----------------|--------|---------------------------------------------------------|-----|

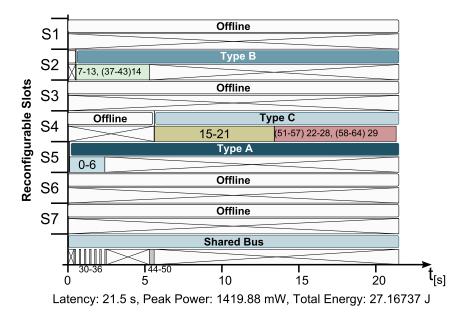

|    |                | 5.3.4  | Case Study C: Resource Management for Dynamic Workloads | 138 |

|    | 5.4            | Summ   | ary                                                     | 143 |

| 6  | Con            | clusio | ns and Future Work                                      | 145 |

|    | 6.1            | Conclu | usions                                                  | 146 |

|    | 6.2            | Main ( | Contributions                                           | 147 |

|    | 6.3            | Future | Work                                                    | 148 |

| Bi | Bibliography 1 |        |                                                         | 151 |

| Pu | blica          | tions  |                                                         | 165 |

## **List of Figures**

| 2.1  | Examples of current multi- and many-core system organizations | ) |

|------|---------------------------------------------------------------|---|

| 2.2  | GRAPHITE for GCC                                              | 4 |

| 2.3  | Polly for LLVM IR                                             | 5 |

| 2.4  | Common spatial prefetching mechanisms                         | 3 |

| 2.5  | AMPM Prefetcher                                               | 7 |

| 2.6  | VLDP Prefetcher                                               | 3 |

| 2.7  | Offset Prefetchers                                            | Э |

| 2.8  | APMC Stream Controller                                        | 1 |

| 2.9  | HotStream Framework DFC                                       | 2 |

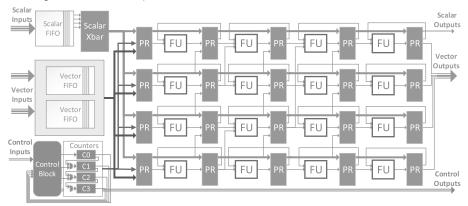

| 2.10 | Plasticine CGRA compute unit                                  | 5 |

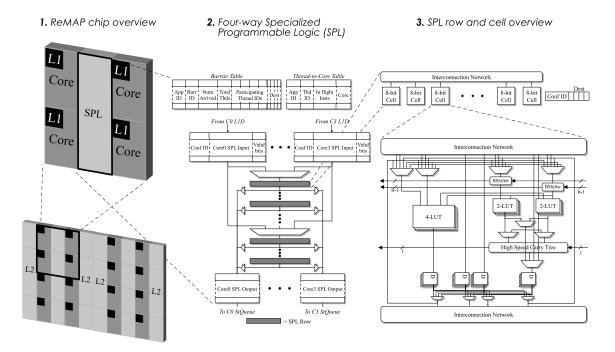

| 2.11 | ReMAP Architecture                                            | 7 |

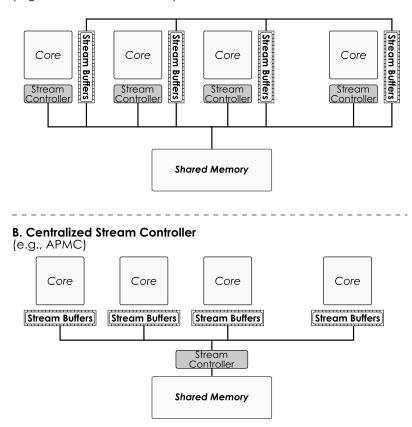

| 3.1  | Stream controller topologies                                  | 4 |

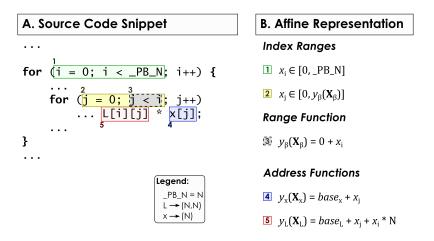

| 3.2  | Example affine representation                                 | 3 |

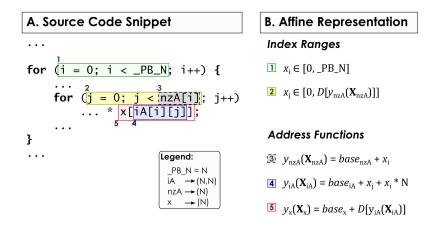

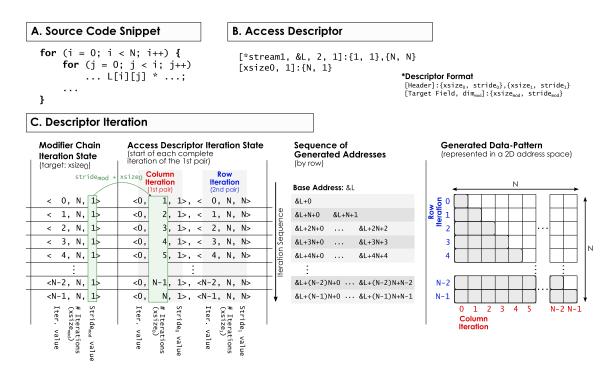

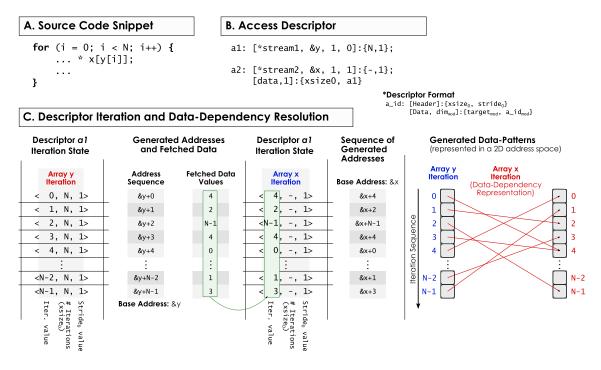

| 3.3  | Example affine representation of indirect memory accesses     | 9 |

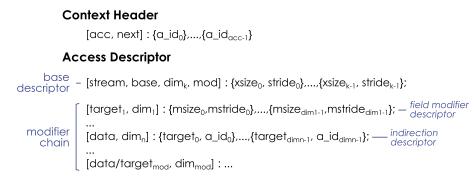

| 3.4  | Context Descriptor specification                              | ) |

| 3.5  | Access Descriptor encoding for a triangular matrix access     | 1 |

| 3.6  | Access Descriptor encoding for indirect memory indexation     | 2 |

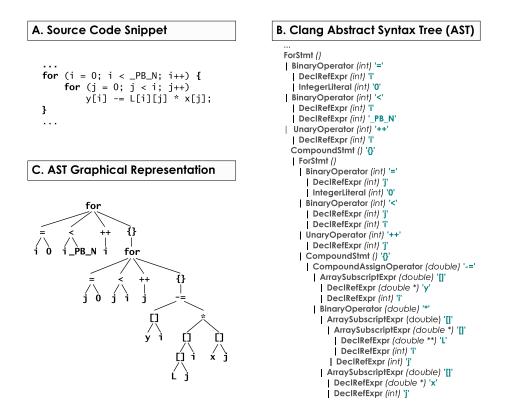

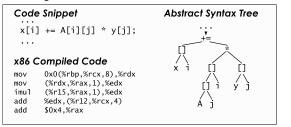

| 3.7  | Clang AST example                                             | 3 |

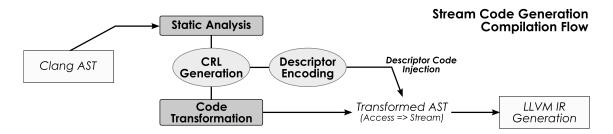

| 3.8  | Overview of the compilation tool                              | 4 |

| 3.9  | Compilation tool translations and code transformations        | 5 |

| 3.10 | Context Representation Language reference 46                  | 6 |

| 3.11 | Example of an AST translation to CRL                          | Э |

| 3.12 | CRL to descriptor representation translation                  | ) |

| 3.13 | Indirection representation and descriptor encoding            | 1 |

| 3.14 | Stream code transformation illustration                       | 2 |

| 3.15 | Considered synthetic data-patterns                            | 7 |

| 3.16 | Context descriptor efficiency 58                              | 3 |

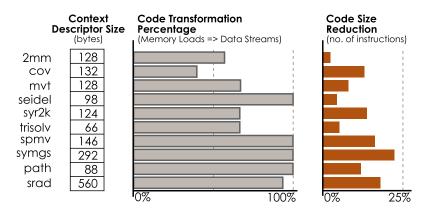

| 4.1  | Data Stream Controller architecture                           | 4 |

| GPU architecture and memory hierarchy overview.                        | 69                   |

|------------------------------------------------------------------------|----------------------|

| Application profiles                                                   | 70                   |

| Stream prefetching mechanism integration                               | 71                   |

| GPU benchmark results                                                  | 74                   |

| CPU integration of the proposed DSC                                    | 75                   |

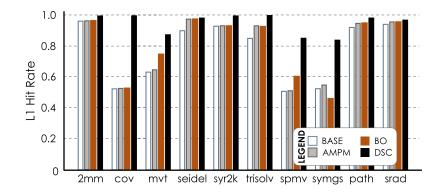

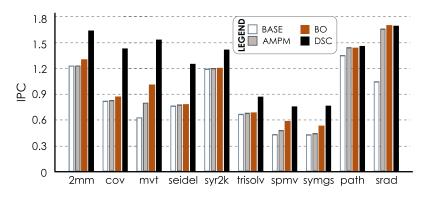

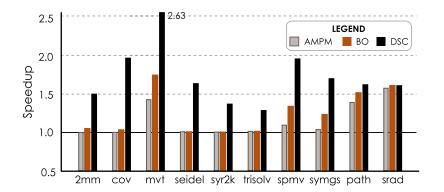

| L1 hit rate comparison                                                 | 80                   |

| IPC comparison in absolute values                                      | 80                   |

| Overall speedup comparison                                             | 81                   |

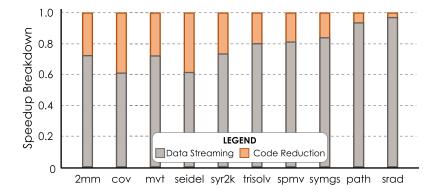

| Speedup breakdown in data streaming and code reduction                 | 81                   |

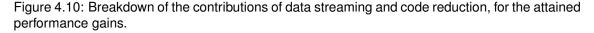

| In-cache stream communication infrastructure overview                  | 84                   |

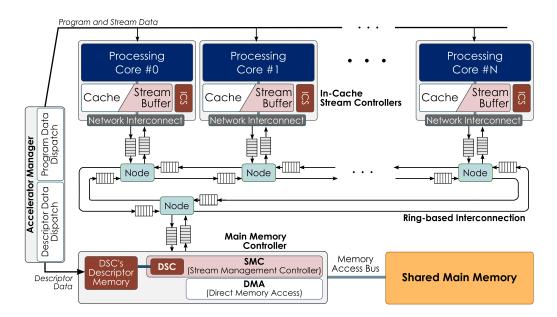

| 2 Cache memory hybridization                                           | 86                   |

| In-cache stream controller architecture                                | 87                   |

| Message-passing protocol                                               | 89                   |

| Memory access optimization illustration                                | 92                   |

| Reorder buffer architecture                                            | 93                   |

| Main memory throughput and memory access latency                       | 99                   |

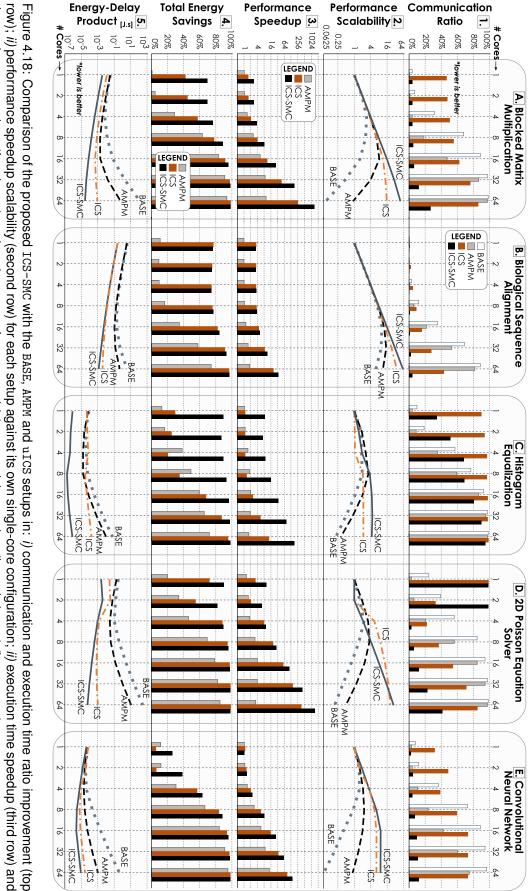

| Comparison of the ICS-SMC with the BASE, AMPM and uICS setups $\ldots$ | 100                  |

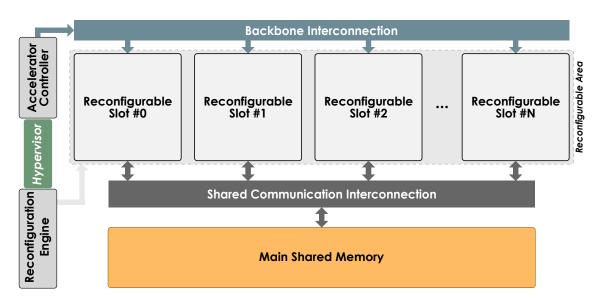

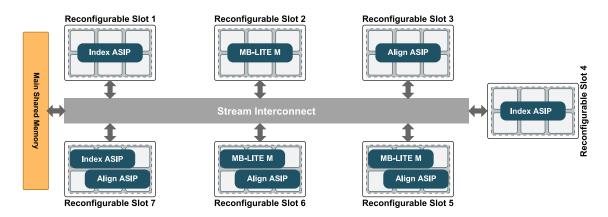

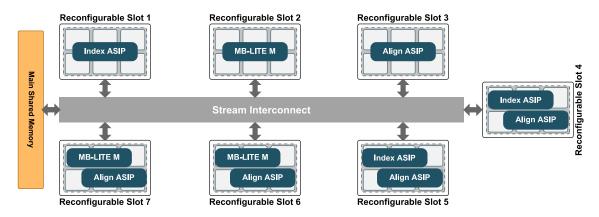

| Reconfigurable many-core accelerator overview                          | 107                  |

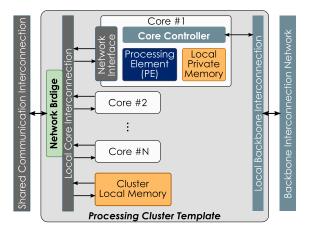

| Internal block diagram of a processing cluster                         | 109                  |

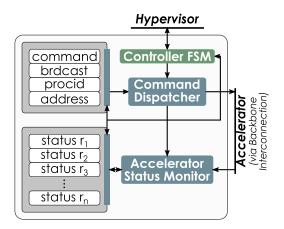

| Accelerator Controller                                                 | 111                  |

| Reconfiguration engine architecture                                    | 112                  |

| Execution plan example                                                 | 120                  |

| Example of a system specification                                      | 121                  |

| Example of an architecture model                                       | 122                  |

| NSGA-II extension                                                      | 123                  |

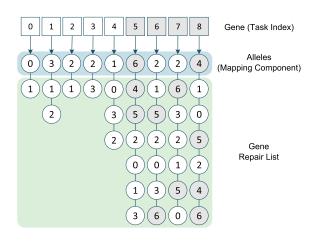

| Individual encoding                                                    | 126                  |

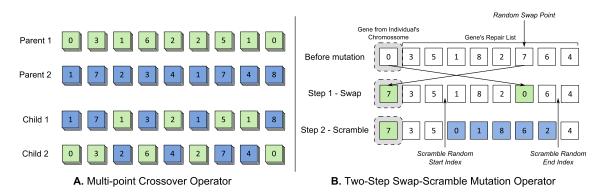

| DSE operators                                                          | 127                  |

| Example of an execution queue                                          | 129                  |

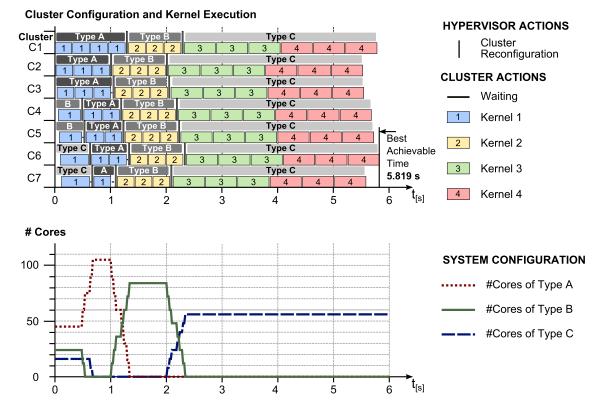

| Real-time adaptation of the processing architecture A                  | 132                  |

| Real-time adaptation of the processing architecture B                  | 132                  |

| System real-time adaptation - Maximum performance                      | 133                  |

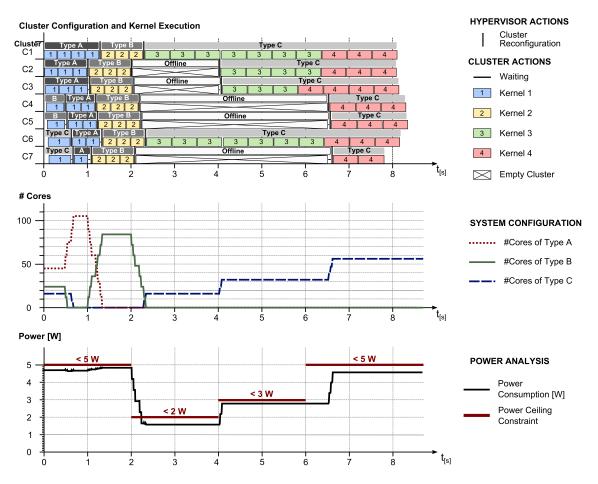

| System real-time adaptation - Power ceiling                            | 134                  |

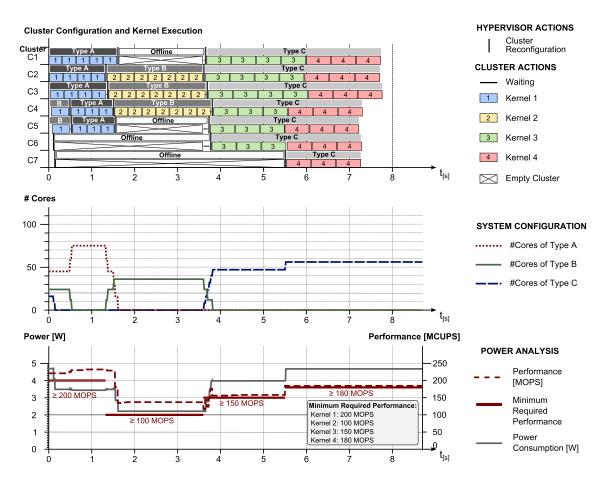

| System real-time adaptation - Minimum performance                      | 135                  |

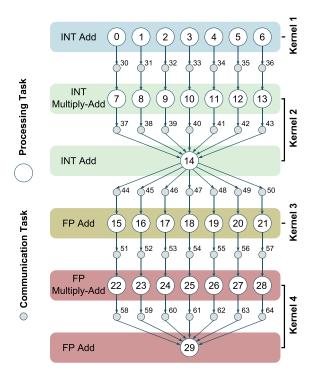

| Arithmetic benchmark application model                                 | 136                  |

| Arithmetic benchmark architecture configuration                        | 136                  |

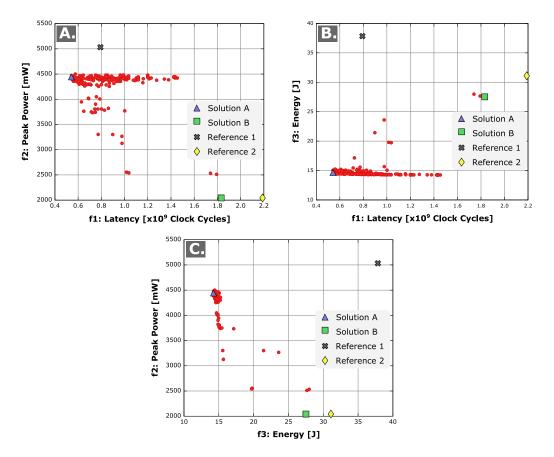

| Objective function interaction in the Pareto front                     | 138                  |

| Execution-time optimization plan                                       | 139                  |

|                                                                        | Application profiles |

| 5.21 Low peak power dissipation optimization plan | 139 |

|---------------------------------------------------|-----|

| 5.22 Biological sequence alignment system model   | 141 |

| 5.23 Relaxed execution plan                       | 143 |

| 5.24 Intensive execution plan                     | 143 |

## **List of Tables**

| 3.1 | Considered standard benchmarks and kernels                           | 55  |

|-----|----------------------------------------------------------------------|-----|

| 3.2 | Characterization of the considered synthetic kernels                 | 57  |

| 4.1 | GPGPU-Sim configuration and benchmark set                            | 73  |

| 4.2 | Adopted x86-based CPU configuration.                                 | 77  |

| 4.3 | Considered benchmarks and kernels for the evaluation setup           | 78  |

| 4.4 | Configurations for the reference prefetching and proposed DSC setups | 79  |

| 4.5 | Benchmark applications and datasets                                  | 96  |

| 4.6 | Resource usage                                                       | 97  |

| 4.7 | Address generation rate and descriptor size                          | 97  |

| 5.1 | Characterization of each type of core                                | 115 |

| 5.2 | Characterization of each cluster type                                | 115 |

| 5.3 | Characterization of the accelerator's supporting infrastructure      | 115 |

| 5.4 | Execution time and energy results                                    | 135 |

| 5.5 | Arithmetic kernel benchmark characterization                         | 137 |

| 5.6 | Biological sequence alignment case study                             | 141 |

## **List of Algorithms**

| 1 | Execution Time Optimization           | 118 |

|---|---------------------------------------|-----|

| 2 | Power-Ceiling Algorithm               | 118 |

| 3 | Minimum Assured Performance Algorithm | 119 |

| 4 | Mapping Validation/Repair Operator    | 127 |

| 5 | Execution Plan Definition Operator    | 128 |

## **List of Acronyms**

| AGU  | Address Generation Unit                        |

|------|------------------------------------------------|

| ALU  | Arithmetic and Logic Unit                      |

| AMPM | Access Map Pattern Matching                    |

| APMC | Advanced Pattern-based Memory Controller       |

| ASIC | Application Specific Integrated Circuit        |

| ASIP | Application Specific Instruction-set Processor |

| AST  | Abstract Syntax Tree                           |

| ССРО | Clock Cycles per Operation                     |

| CGRA | Coarse-Grained Reconfigurable Array            |

| CLB  | Configurable Logic Block                       |

| CPU  | Central Processing Unit                        |

| CRL  | Context Representation Language                |

| СТА  | Cooperative Thread Array                       |

| DFC  | Data-Fetch Controller                          |

| DMA  | Direct Memory Access                           |

| DSC  | Data Stream Controller                         |

| DSE  | Design Space Exploration                       |

| DSP  | Digital Signal Processor                       |

| DVFS | Dynamic Voltage and Frequency Scaling          |

| EA   | Evolutionary Algorithm                         |

| EDP  | Energy-Delay Product                           |

| FIFO    | First-In First-Out                         |

|---------|--------------------------------------------|

| FP      | Floating-Point                             |

| FPGA    | Field-Programmable Gate Array              |

| FPU     | Floating-Point Unit                        |

| FSM     | Finite-State Machine                       |

| GCC     | GNU Compiler Collection                    |

| GHB     | Global History Buffer                      |

| GPP     | General Purpose Processor                  |

| GPU     | Graphics Processing Unit                   |

| HPC     | High-Performance Computing                 |

| IC      | Integrated Circuit                         |

| ICAP    | Internal Configuration Access Port         |

| ICS     | In-Cache Stream                            |

| ISA     | Instruction Set Architecture               |

| ISB     | Irregular Stream Buffer                    |

| юТ      | Internet-of-Things                         |

| IPC     | instructions-per-cycle                     |

| IR      | Intermediate Representation                |

| LRU     | Least Recently Used                        |

| LUT     | Look-Up Table                              |

| MCU     | Modifier Chain Unit                        |

| MOEA    | Multi-Objective Evolutionary Algorithm     |

| MOO     | Multi-Objective Optimization               |

| MSHR    | Miss Status Hold Register                  |

| NoC     | Network on Chip                            |

| NSGA-II | Non-dominated Sorting Genetic Algorithm II |

- NVM Non-Volatile Memory

- **OPS** operations-per-second

- PARE Power-Aware pRefetch Engine

- PC Program Counter

- PE Processing Element

- **RISC** Reduced Instruction Set Computer

- SIMD Single-Instruction Multiple-Data

- SIMT Single-Instruction Multiple-Thread

- SM Streaming Multiprocessor

- SMC Stream Management Controller

- SoC System-On-Chip

- TLB Translation Lookaside Buffer

- VLDP Variable Length Delta Prefetcher

- VLIW Very Long Instruction Word

#

## Introduction

#### Contents

| 1.1 | Motivation and Objectives | 3 |

|-----|---------------------------|---|

| 1.2 | Contributions             | 5 |

| 1.3 | Outline                   | 7 |

The ever-increasing demand for computational processing power has reached a critical point in the past decade since the straightforward scaling of current technology is no longer viable [1]. Moreover, driven by the Internet-of-Things (IoT) and Cloud Computing era, an ever-increasing number of computing platforms, ranging from battery-powered mobile devices to supercomputing clusters, has been hitting the limits of performance and energy efficiency. In fact, computing efficiency has been recognized as the most challenging goal to achieve cost-effective *exascale computing* by 2020 (as established by the High-Performance Computing (HPC) community) [2]. Accordingly, the scientific community recognizes that the research on new node/chip-level architectures, circuitry management mechanisms and memory packaging technologies, represents promising strategies that can still contribute an estimated 5x improvement in performance and energy efficiency [3].

To attain such a goal, the computing market has been pushing the research on alternative heterogeneous and high-performance many-core processing systems, that combine multiple architectures (with different degrees of parallelism and specialization) to improve the system's processing efficiency. By deploying resource and power management mechanisms, they can balance raw performance and energy consumption according to the aimed execution context. However, processing systems are still struggling to provide the required levels of computing efficiency and reach the *exascale* goal. In fact, their attainable performance is still limited by energy consumption constraints and by the adverse impact of stalls resulting from long memory access latencies.

Specifically, computing throughput is still limited in many computing systems by power supply management mechanisms that turn off parts of the device to save energy, effectively reducing the amount of available processing resources. Moreover, their general purpose nature imposes a processing throughput limit, caused by a gap between flexibility and specialization to the application processing requirements. On the other hand, most systems are still relying on conventional cache-based memory subsystems. However, although they have been widely exploited to reduce the impact of long memory access latencies, the limitations and contention issues of cache structures are well-known [4], as their performance is bound by the characteristics of the application data access pattern.

Accordingly, knowing an application's characteristics (e.g., type of computing operations, the degree of parallelism or memory access patterns) can provide the necessary insights to make its execution as efficient as possible. Such a premise has long been exploited by compilation tools to optimize machine code according to the features of the target architecture [5–10] and by power management and performance throttling mechanisms to reduce energy consumptions [11–15]. It is also the basis for memory access optimization mechanisms (such as data prefetchers [16–24]) that analyze the data indexing behavior of a running application to predict future accesses. However, such solutions are mostly used to mitigate execution and energy overheads or costly data operations and are bound by the general purpose computing nature of off-the-shelf systems.

On the other hand, while application-specific approaches can be tailored according to an application's characteristics to provide the necessary computing efficiency, their inherent loss in flexibility makes them unsuited for the diverse HPC market.

One viable approach to bridge this performance-efficiency gap is the introduction of runtime adaptation in general purpose multi/many-core infrastructures. Specifically, by performing analyses of the application at compile-time and/or at runtime, it is possible to extract its computational requirements and data access characteristics and adapt its execution by: *i*) performing independent data acquisition operations according to its memory access pattern; *ii*) adapt the data communication scheme between the system's processing cores and the main memory; *iii*) perform hardware adaptation of the cores according to the type of executed operations; and *iv*) manage the type and amount of active processing resources according to the system's execution context.

Accordingly, by demarking themselves from off-the-shelf approaches that solely try to hide or mitigate known performance limitations in conventional systems, alternative solutions can be designed that exploit the adaptation of a processing system and modify its infrastructure to meet the running application requirements, without eliminating the system's general purpose computing capabilities. Such solutions can be attained by the combination of compile-time application analysis and optimization tools and the introduction of dynamically reconfigurable architectures and adaptable data communication structures in conventional processing systems. Such structures can also be paired with intelligent execution management modules that leverage the information provided by the compilation tools, with the goal of increasing the system's processing throughput and reducing its energy consumption, in turn increasing the overall computing efficiency.

#### 1.1 Motivation and Objectives

Embracing the energy-efficiency constraints and the current HPC demands, multi-core heterogeneous systems are usually composed of differently balanced architectures to maintain higher levels of performance available while providing low-power execution contexts [12, 15]. Despite being now widely deployed in mobile platforms, such systems still rely on mechanisms based on task migration and aggressive voltage scaling and power-gating. As such, they may require that some (usually most) of the transistors remain dimmed or powered down most of the time, due to the observed divergence between device-level energy efficiency and transistor density [1], in turn pushing the dark silicon problem in current computing systems. Such a problem adds an inefficient utilization of the available processing resources on top of the overheads that are also imposed by task migration mechanisms.

Conversely, application-specific accelerators [25–28] have shown to be capable of leading to high application acceleration with low power supply demands. Such an efficiency often results from the significantly lower architectural footprints and low power dissipation characteristics of

such structures, when compared to conventional processing systems. However, the provided specialization often incurs in a loss in general purpose computing capabilities. Moreover, each system must be tailored to a particular application domain and applications must be carefully dimensioned to exploit as much performance-energy efficiency as possible [28].

However, the actual throughput that is offered by modern computing systems is currently limited by the power/performance impact of data transfers and general data indexing in the memory subsystem. This is a result of the standard adoption of conventional local (and often multi-level) cache structures to avoid high memory access latencies. Although they can significantly reduce latency in the presence of computationally intensive applications, they struggle when the application is bound by the characteristics of its memory accesses. Hierarchical cache structures especially struggle when the application dataset is large and does not fit in one or more cache levels, or in the presence of complex memory access patterns, where data-locality cannot be efficiently exploited.

Typically, the first steps to mitigate the impact of long memory access latencies are performed at compile-time. In particular, compilers have long utilized specialized tools to reorganize an application's sequence of instructions and hide memory access latency behind computation [29, 30]. The deployed algorithms statically analyze the original code and optimize it, with the goal of bridging the gap between application code characteristics and the capabilities of the target processing architecture and memory subsystem [5–10].

By following a similar principle, data prefetching techniques [16–19, 19–24, 31–33] are designed to deal with the intrinsic characteristics of the memory access patterns at runtime. In particular, they analyze an application's sequence of memory requests to predict future accesses and obtain data ahead of time, hence mitigating the impact of long memory access latencies. However, despite their throughput improvements, the incremental gains provided by each new generation of prefetchers are becoming limited. This is mostly because prediction inaccuracies can still occur when dealing with complex data patterns, which affect the memory access coverage. On the other hand, they must rely on costly runtime memory access monitoring, which can result in added time-consuming penalties.

Furthermore, to achieve higher prediction accuracies, such data prefetching schemes not only require larger amounts of hardware resources to implement the predictive algorithm but also added memory space to trace recent accesses [20, 22–24]. Moreover, when applied to processing systems with large numbers of physical cores, the prefetching structures can suffer from the same increased contention that occurs with conventional cache-based systems, resulting from a flood of prefetching requests in the memory subsystem [16].

Accordingly, by considering that application-specific architectures have limited use in a general purpose HPC context, **adaptive computing systems** (exploiting hardware reconfiguration and dynamic data communication schemes) represent a promising approach to provide the nec-

4

essary mechanisms to bridge that gap and to push the limits of **computing efficiency**. Naturally, the viability of such adaptive systems implies that the running application is thoroughly analyzed by compiler tools that can extract information regarding its computational requirements (including, but not limited to, types of processing operations, instruction and data parallelism, data communication schemes and memory access patterns) and provide it to the system's processing infrastructure, so it can adapt itself to the execution context and improve its overall performance and energy efficiency.

Acknowledging that conventional processing systems and memory organizations are hardly coping with the throughput demands of current applications and with the challenges recognized by the HPC community, the main objective of this thesis is the investigation of new adaptive computing techniques and mechanisms (acting both at compile-time and runtime) to provide the means to improve the performance and energy efficiency of future generations of computing systems.

#### 1.2 Contributions

To attain the described objectives, the presented research is initially focused on compile-time memory access pattern analysis and encoding, combined with code transformations, to enable data stream communication in conventional cache-based infrastructures. Such mechanisms allow the exploitation of new data communication and stream prefetching schemes, resulting in runtime data movement adaptation and memory throughput maximization. The same principle of compile-time application analysis and optimization is also explored for reconfigurable processing acceleration through a comprehensive study on runtime architecture adaptation. In the particular context of Field-Programmable Gate Array (FPGA) implementation technologies, it is explored the viability of using partial reconfiguration to increase the processing efficiency. This mechanism is used as an alternative to voltage/frequency scaling and power/clock-gating mechanisms to deploy throughput-energy balancing mechanisms to improve overall computing efficiency.

Accordingly, the contributions of this Thesis can be summarized in the following paragraphs, together with the enumeration of the resulting publications in peer-reviewed journals and conferences where these contributions were made available to the scientific community:

- A memory access description specification, based on a multi-level affine model that allows the encoding of data dependencies between accesses. This specification is capable of efficiently encoding memory access patterns through improved description flexibility and efficiency, providing support for arbitrarily complex deterministic access patterns and indirect memory accesses;

- N. Neves, P. Tomás, and N. Roma, "Efficient data-stream management for sharedmemory many-core systems," in <u>25th International Conference on Field Programmable</u> <u>Logic and Applications (FPL)</u>. IEEE, 2015, pp. 508–515

- N. Neves, P. Tomás, and N. Roma, "Adaptive in-cache streaming for efficient data management," <u>IEEE Transactions on Very Large Scale Integration (VLSI) Systems</u>, vol. 25, no. 7, pp. 2130–2143, March 2017

- N. Neves, P. Tomás, and N. Roma, "Stream data prefetcher for the gpu memory interface," The Journal of Supercomputing, vol. 74, no. 76, pp. 2314–2328, June 2018

- A compile-time static analysis tool to identify, describe and encode the application's memory

access pattern using the proposed representation. As a result of this data access encoding,

the explicit representation of the memory access pattern makes the corresponding data indexation and address calculation redundant and unnecessary. Accordingly, the compilation

tool also performs a code transformation pass that replaces the array subscript indexation

of each encoded data load with a stream reference (represented by a pointer), ultimately

resulting in a reduced number of instructions and accelerating the execution of the code;

- A new In-Cache Stream (ICS) communication model supporting both *memory-addressed* and *packed-stream* data accesses, as well as adaptive mixed *memory-addressed/packed-stream* accesses, specially suited for applications composed of compile-time predictable (described as a set of streams) and non-predictable memory access patterns. The physical implementation of the ICS model also deploys several efficient memory access optimization techniques, such as bandwidth optimization, data reorganization and reutilization, and intime stream manipulation;

- N. Neves, A. Mussio, F. Gonçalves, P. Tomás, and N. Roma, "In-cache streaming: Morphable infrastructure for many-core processing systems," in <u>Euro-Par 2016: Parallel</u> Processing Workshops. Springer International Publishing, 2017, pp. 775–787

- N. Neves, P. Tomás, and N. Roma, "Adaptive in-cache streaming for efficient data management," <u>IEEE Transactions on Very Large Scale Integration (VLSI) Systems</u>, vol. 25, no. 7, pp. 2130–2143, March 2017

- A reconfigurable hundred-core heterogeneous architecture, capable of adapting its processing characteristics according to runtime application requirements. This architecture is particularly suited to take advantage of the partial dynamic reconfiguration capabilities of modern FPGA devices. The system is capable of autonomously determining and reconfiguring each processing core to the most suitable architecture through a set of runtime optimization policies to balance the number and micro-architecture of the instantiated cores, according to instantaneous application and system requirements and constraints;

- N. Neves, H. Mendes, R. J. Chaves, P. Tomás, and N. Roma, "Morphable hundred-core heterogeneous architecture for energy-aware computation," <u>IET Computers & Digital</u> <u>Techniques</u>, vol. 9, no. 1, pp. 49–62, 2015

- N. Neves, P. Tomás, and N. Roma, "Host to accelerator interfacing framework for highthroughput co-processing systems," in XI Jornadas sobre Sistemas Reconfiguráveis

(REC), 2015, pp. 31-38

- A compile-time analysis and optimization tool for efficient scheduling and mapping of processing tasks into reconfigurable architectures. The conceived tool is based on a combination of Multi-Objective Optimization (MOO) and Design Space Exploration (DSE) techniques and is capable of deriving multiple sets of adaptive task mapping plans, which establish different compromises between the application's performance, system power consumption, and energy efficiency.

- N. Neves, R. Neves, N. Horta, P. Tomás, and N. Roma, "Multi-objective kernel mapping and scheduling for morphable many-core architectures," <u>Expert Systems with</u> <u>Applications</u>, vol. 45, pp. 385–399, 2016

#### 1.3 Outline

The dissertation is organized in the following chapters. After this introductory part, Chapter 2 presents a revision of the current state-of-the-art and technical background in the research domains related to application analysis, data prefetching, data-stream and adaptive communication techniques, and reconfigurable processing systems. The new memory access description specification is detailed in Chapter 3, together with the conceived static analysis and code transformation tools. Chapter 4 describes the proposed data streaming mechanisms and their implementation and evaluation in a Graphics Processing Unit (GPU), in a General Purpose Processor (GPP) and an FPGA accelerator, together with comprehensive comparisons with state-of-the-art solutions. Chapter 5 presents a study on dynamically adaptable processing architectures and describes the implementation of a fully functional reconfigurable accelerator prototype. The study is complemented with the implementation of a DSE compile-time optimization tool to support the task scheduling and mapping into reconfigurable hardware. Finally, a discussion of the achieved contributions is presented in Chapter 6, together with the enumeration of some possible future research guidelines.

# 2

## **Background and State-of-the-Art**

#### Contents

| 2.1 | Overview of Modern Computing Systems                                 |

|-----|----------------------------------------------------------------------|

| 2.2 | Data Communication Schemes and Paradigms                             |

|     | 2.2.1 Compiler Static Analysis and Memory Access Optimization        |

|     | 2.2.2 Data Prefetching Techniques                                    |

|     | 2.2.3 Data Streaming Architectures                                   |

|     | 2.2.4 Discussion                                                     |

| 2.3 | Adaptive Computing                                                   |

|     | 2.3.1 Power Supply Management                                        |

|     | 2.3.2 Dynamically Reconfigurable Systems                             |

|     | 2.3.3 Dedicated Programming Frameworks and Execution Optimization 28 |

|     | 2.3.4 Reconfigurable Communication Systems                           |

|     | 2.3.5 Discussion                                                     |

| 2.4 | Summary                                                              |

This chapter provides a brief overview of the currently prominent computing system architectures, followed by a review of the most important state-of-the-art approaches in the areas of reconfigurable computing architectures and data communication techniques and infrastructures.

#### 2.1 Overview of Modern Computing Systems

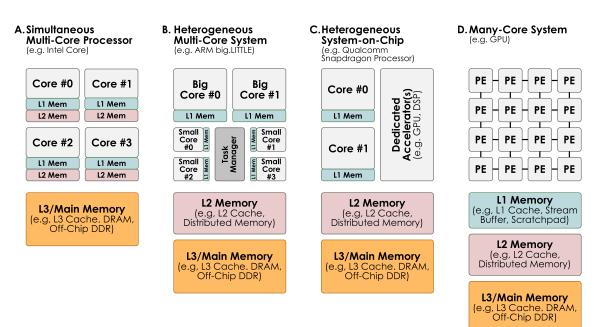

Since the decay of the single-core General Purpose Processor (GPP) era that chip power consumption has been regarded as one of the most pressing concerns in the development of modern High-Performance Computing (HPC) architectures. Acknowledging that raw processing power inevitably leads to high energy consumption, early solutions relied on the complexity reduction of general-purpose processing architectures and their replication in multi-core infrastructures (depicted in Fig. 2.1.A), allied with voltage and operating frequency management techniques (e.g., power-gating or Dynamic Voltage and Frequency Scaling (DVFS)). However, such a lower structural complexity led to reduced processing capabilities per core, thus limiting the achievable core performance as a trade-off for lower energy consumptions.

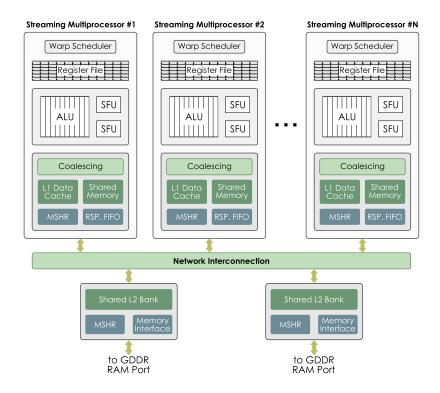

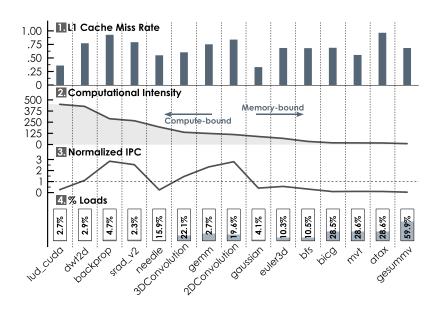

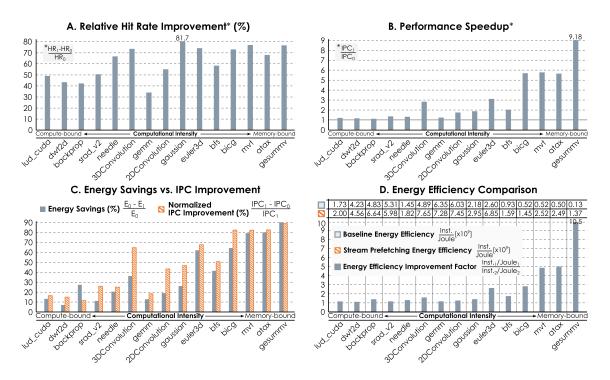

Accordingly, several current solutions try to surpass this per-core lower performance with increased levels of parallelism. This is often done by deploying infrastructures with large numbers of processing cores, either on the same chip (such as Graphics Processing Units (GPUs), as depicted in Fig.2.1.D) or by interconnecting several processors (such as data-center clusters). However, the increased number of processing units incurs, by itself, on added energy consumption in the whole system. This is due to the amount of logic required to deploy and control massively parallel architectures and the underlying data communication infrastructures.

Figure 2.1: Examples of current multi- and many-core system organizations.

To circumvent this issue, instead of massively parallelizing architectures to increase raw performance, heterogeneous systems with different co-existing architectures have been regarded as viable solutions. Such systems are often based on combinations of both high-performance and low-power general-purpose architectures or on the deployment of System-On-Chips (SoCs) combining several different dedicated architectures on a single chip, as depicted in Figs. 2.1.B and 2.1.C. While the first approach allows a precise balance between processing performance and energy consumption, the latter acknowledges that specialized architectures lead to straightforward application accelerations (with low power dissipation) [25]. This results in significantly lower energy consumptions, often aided by the lower architectural footprint and power dissipation characteristics of those processing structures. Nevertheless, despite the broad range of dedicated architectures that can be deployed in heterogeneous systems (e.g., GPPs, Digital Signal Processors (DSPs), GPUs, mobile communication or localization modules), such a specialization often incurs in a loss in general-purpose computing capabilities. Moreover, each system must be tailored to a particular application domain, and each task has to be scheduled and migrated to its corresponding dedicated architecture. In fact, since each computing unit is usually best-suited to run a specific type of application, the amount of existing dedicated architectures and parallelism require a careful balance to avoid long module power-down times [1].

The recent reemergence of reconfigurable systems [41–44] has driven the development of alternative mechanisms to deploy dynamic processing specialization while achieving a more efficient resource utilization. Instead of turning off specific processors (or processor components), leaving part of the device unused, reconfigurable architectures reuse the same resource area to provide different dedicated processing structures and schemes to better suit several applications and system constraints. Hence, they can provide the means to make the execution as efficient as possible, both in terms of performance and energy consumption [45–48]. Furthermore, by adopting such structures, it is possible to achieve throughput and efficiency levels similar to those offered by application-specific accelerators [49], without losing general-purpose computing capabilities.

However, although reconfigurable architectures can provide higher levels of processing efficiency, the design of such architectures is usually focused on the processing blocks and their adaptation, often neglecting the power/performance impact of data transfers and general data indexing in the memory subsystem. A standard approach to tackle this problem is to only rely on conventional local (and often multi-level) cache structures (as depicted in Fig. 2.1) to avoid high memory access latencies. However, as the number of cores on a cache-coherent system increases, its contention and overall energy consumption tend to grow. As a result, it can even reach a point where the addition of more cores is no longer useful [4], hence limiting the system's achievable processing throughput. Moreover, such structures struggle when the application dataset is very large and does not fit in the cache, or in the presence of complex memory access

11

patterns, where data-locality cannot be efficiently exploited.

Nevertheless, some adaptive schemes targeting energy efficiency have already been deployed in the communication infrastructure [50–52]. However, they mostly focus on the management of memory resources, to reduce energy consumption through architectural adaptation. Although it has been proved viable for processing infrastructures, the communication infrastructures struggle to efficiently exploit the advantages of adaptive mechanisms (e.g., attained by dynamic reconfiguration or gating mechanisms). This is mostly due to the fact that data communication in many-core infrastructures is already itself constrained in what concerns data transfer latency, mainly resulting from its high contention and request concurrency. Hence, the potential overheads that would result from adapting the communication infrastructure not only would impose additional latency constraints but also would require a careful synchronization between the data transfers and the adaptation process, to avoid data losses and coherency/consistency issues.

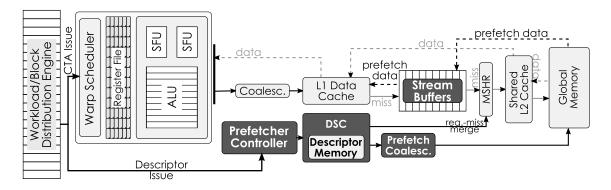

Conversely, data prefetching techniques have recently reemerged [18–21] as viable solutions to optimize the sequence of issued memory requests and to mitigate the impact of long memory access latencies. Several methods have been designed to deal with the intrinsic characteristics of the memory access patterns, such as reduced data-locality [21, 31], complex access patterns [17, 19, 32, 33] or large datasets that do not fit in the cache [53]. Moreover, due to their successful memory access improvements, a wide range of device classes has been targeted, from typical multi-core GPP architectures [17] to GPU devices [16]. In fact, this technology has evolved to a point where the main concern is no longer memory access pattern detection and prediction, but instead the timeliness and effectiveness of the prefetching procedure. This led to the emergence of new prefetchers [20, 22–24] that combine multiple hardware modules, with different data fetch granularities and prediction heuristics, across different cache levels.

However, despite the improved throughput, the gains provided by each new generation of prefetchers are becoming limited. In particular, depending on the complexity of the prefetcher, prediction inaccuracies can still occur when dealing with complex data patterns, which affect the memory access coverage and can result in time-consuming penalties. Hence, instead of mitigating memory access latencies, such drawbacks can result in added pressure to the memory subsystem. On the other hand, if a prefetcher deploys more sophisticated techniques to achieve higher prefetching accuracies, it not only utilizes larger amounts of hardware resources to implement the predictive algorithm, but it also requires added memory space to trace recent accesses [20, 22–24]. Furthermore, when applied to processing systems with high levels of parallelism (i.e., with large numbers of physical cores), the prefetching structures tend to require precise synchronization mechanisms and intensity balancing [16]. Otherwise, they can suffer from the same increased contention that occurs with conventional cache-based systems, resulting from a flood of prefetching requests in the memory subsystem.

To circumvent such issues, stream-based communication schemes have been regarded as a

viable alternative to cache-based systems and pure-prefetching structures [26, 34, 54]. Instead of having a processing core performing its main memory requests, they are based on the principle that it is possible to exploit the memory access pattern to transparently buffer and transmit (*stream*) the requested data to the corresponding core. Hence, by explicitly decoupling the data indexation/communication and processing infrastructures, data transfers can effectively be hidden behind computation, in turn decreasing the data transfer path and counteracting most of the contention observed in the shared communication structures.

However, due to their application-specific nature, streaming architectures have only been deployed in custom dedicated accelerators [26, 27, 34]. Moreover, they typically require the programmer to manually encode the memory access pattern corresponding to each data stream. Hence, without proper compilation tools, its viability becomes limited for general purpose contexts. Furthermore, since an accurate memory access pattern description is limited to applications with arbitrarily complex, but still deterministic, memory access patterns, purely stream-based infrastructures can hardly deal with certain types of applications. As an example, they struggle in the presence of pointer-based data structures or dynamic indexing procedures, where the memory access is either non-deterministic or generated at runtime. As such, they need to be combined with conventional communication schemes to efficiently handle such cases without relying on costly runtime memory access monitoring [54] and heuristic predictions [18].

# 2.2 Data Communication Schemes and Paradigms

While performance and efficiency are typically sought by improving the system's processing infrastructure, by making the computing architecture as fast and efficient as possible, the offered throughput is still often limited by the impact of data transfers and general data indexing. This is because the computing architecture in most systems can perform elementary operations much faster than the time that is required to obtain data from the main memory. This data acquisition latency is particularly high when off-chip memory modules are accessed and can lead to considerable performance losses.

Typically, a preliminary mitigation of the impact of costly memory accesses is performed at compile-time, by analyzing the sequence of instructions of an application. According to the target architecture, the compiler performs instruction reorganizations to try to hide the high latency of memory accesses behind other computational instructions, hence promoting instruction-level and data-level parallelism.

On the other hand, at the hardware level, different communication paradigms have been adopted to minimize the power/performance impact of the data management subsystem. In particular, besides straightforward and aggressive data prefetching schemes, often associated with high-energy consuming memory/cache hierarchies, more efficient and sophisticated stream-

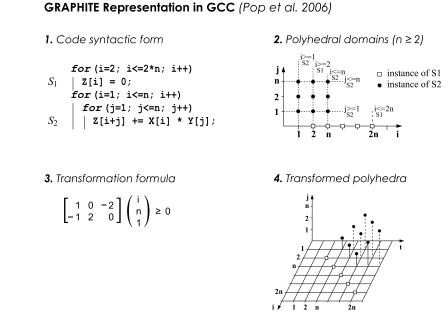

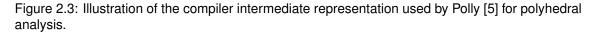

Figure 2.2: Illustration of the compiler intermediate representation used by GRAPHITE [6] for polyhedral analysis.

based communication systems have been explored. This section presents a review of the most prominent compiler tools and data prefetching and streaming solutions.

# 2.2.1 Compiler Static Analysis and Memory Access Optimization

Historically, compilation tools have been used to optimize the sequence of computational operations and hide memory access latency behind computation, bridging the gap between application code characteristics and the capabilities of the target processing architecture. Sophisticated compiler tools often rely on static code analysis [5–7] to extract application information regarding instruction/data dependencies, memory access patterns and/or critical instructions [8]. With this information, these tools subsequently apply code transformations to perform data access reorganization [8, 10] or code optimizations [9], with the goal of increasing instruction-level parallelism to hide the memory access latency. Moreover, the information provided by the compiler is also often used at runtime for assisted execution [8] and/or assisted data acquisition schemes [18, 53].

# 2.2.1.A Polyhedral Analysis

Compilers have long adopted the polyhedral model to represent nested-loop programs [30]. It is based on the assumption that each loop iteration (within a nested loop) can be described as a lattice point inside mathematical objects called polyhedra (see Fig. 2.2-2). Such a representation allows the compiler to perform affine transformations over the original code and generate optimized loop nests according to an optimization goal (such as vectorization or parallelization).

In an early approach, Pop et al. [6] recognized that polyhedral analysis and loop nest trans-

#### Polyhedral Analysis in LLVM (Grosser et al. 2011)

| 1. Code syntactic form                                                                                                                                                | 3. LLVM-IR                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>for (i = 0; i &lt; 100; i++) S4: K[2*i] = 3;</pre>                                                                                                               | <pre>bb:<br/>br label%bb1<br/>bb1: ; Basic block of S4<br/>%indvar = phi i64 [ 0, %bb ], [ %indvar.next, %bb1 ]</pre>                                                                                                                                                                                                                             |

| <b>2.</b> Polyhedral representation<br>$D_{S4} = \{S4[i] : 0 \le i \le 100\}$<br>$S_{S4} = \{S4[i] \rightarrow [0, i, 0]\}$<br>$A_{S4} = \{S4[i] \rightarrow K[2i]\}$ | <pre>; %indvar -&gt; {0,+,1}&lt;%bb1&gt; %tmp = muli64 %indvar, 2 %gep = getelementptr[100 x float]* @K, i64 0, i64 %tmp ; %gep -&gt; {@K,+, (2 * sizeof(float))}&lt;%bb1&gt; store float 3.00000e+00, float * %gep, align8 %indvar.next = addi64 %indvar, 1 %exitcond = icmpeq i64 %indvar.next, 100 br il %exitcond, label%bb2, label%bb1</pre> |

|                                                                                                                                                                       | bb2:<br>ret void<br>; Loop %bb1: backedge-taken count is 99                                                                                                                                                                                                                                                                                       |

formations are affordable approaches in production compilers. They proposed the GRAPHITE intermediate representation for the GCC compiler [29] (see Fig. 2.2). It combined static analysis with code transformations to effectively balance compilation time reduction and analysis precision. Inspired by this early work, Grosser et al. [5] applied the same principle to the LLVM compiler [30] (see Fig. 2.3), by recognizing that polyhedral techniques were limited to simple programs and specific programming languages. Accordingly, they proposed Polly to automatically detect and transform relevant parts of each program in a language-independent and syntactically transparent way. It deployed an advanced data dependency analysis and support for external optimizers and most common programming languages and compilation targets (such as Central Processing Units (CPUs), GPUs and hardware descriptions).

## 2.2.1.B Parallel Code Optimization

Other tools have also addressed the increased data transfer contention that characterizes multi-core processors. Majo et al. [7] presented a study showing that many loop-parallel programs include mutually incompatible data access patterns that can result in a high fraction of costly memory accesses. They proposed a set of language-level primitives for memory allocation and loop scheduling, that are used together with simple program-level transformations to eliminate mutually incompatible access patterns from OpenMP-style parallel programs. Similarly, Kiriansky et al. [10] recognized that traditional compiler cache optimizations have not been sufficiently aggressive to overcome the poor scaling of memory bandwidth in parallel applications. Accordingly, they introduced the *milk* language extension to allow programmers to annotate memory-bound loops for efficient parallelization with OpenMP. They used intermediate data structures to transform random indirect memory references into batches of efficient sequential memory accesses.

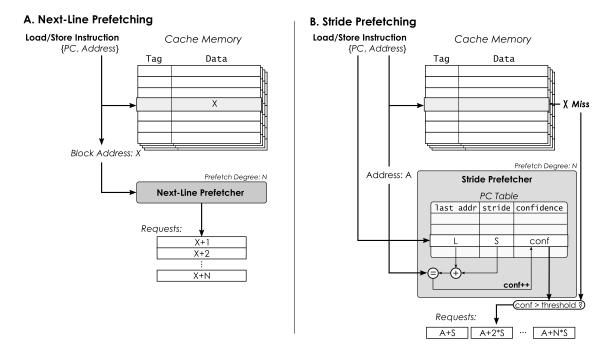

Figure 2.4: Common spatial prefetching mechanisms.

# 2.2.2 Data Prefetching Techniques

With the existing contention issues of conventional cache-based systems and shared communication infrastructures, prefetching had a strong reemergence in the past decade with the exploration and combination of several new sophisticated techniques. Such methods are particularly designed to deal with the intrinsic characteristics of particular types of applications, such as reduced data-locality and complex memory access patterns, memory-bound kernels or very large datasets that do not fit in the local memories.

Several solutions have been designed, by trading-off hardware complexity (area resources and power dissipation), prefetching intensity (degree of fetch requests to future addresses), accuracy (rate of correct fetch requests) and coverage (amount of prefetched data in the total dataset). Hence, to maximize the accuracy and the attained coverage (and consequently, the system's throughput), they must rely on complex dedicated modules that dynamically analyze the most recent memory access patterns and try to predict future accesses based on heuristic algorithms. A selected list of techniques is presented in the next paragraphs.

# 2.2.2.A Spatial Prefetching

Just as caches, the simpler and most common prefetching solutions, take advantage of the memory access spatial locality. By following this principle, sequential prefetchers try to preempt data accesses by populating the cache with several lines ahead of the most recently accessed address. In this category, *next-line prefetchers* (see Fig. 2.4.A) work by aligning a requested address to its corresponding block (cache line) address and then requesting the next *N* subsequent

#### Access Map Pattern Matching Prefetcher (Ishii et al. 2011)

Figure 2.5: Temporal-based prefetching mechanism of the AMPM prefetcher [20].

lines (prefetch degree) from the memory hierarchy level.

Naturally, being this a hardly practical approach, the slightly more efficient *stride prefetchers* analyze the most recently requested addresses and calculate the difference between them (stride) to predict future accesses (see Fig. 2.4.B). To infer the correct sequence of addresses, these prefetchers typically rely on the use of prediction table structures indexed by the instruction address (Program Counter (PC)). As such, for each load/store instruction they register the last accessed address, the difference between subsequently accessed addresses (stride) and a confidence value (incremented every time the difference between addresses matches the calculated stride). When the confidence value reaches a predefined threshold the prefetcher issues requests to the next *N* strided addresses (as depicted in Fig. 2.4.B).

## 2.2.2.B Temporal Prefetching

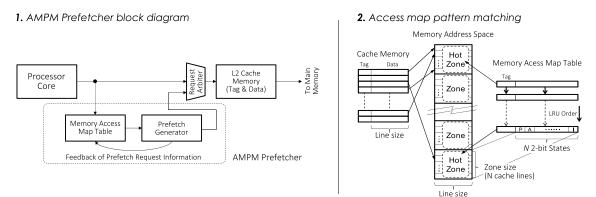

Since memory access patterns can present characteristics more complex that strided address sequences [20], spatial prefetching approaches are often enhanced with temporal-locality-based heuristic prediction schemes to increase the achievable prefetch coverage. By following that principle, Ishii et al. [20] proposed the Access Map Pattern Matching (AMPM) prefetcher (see Fig. 2.5) to identify hot zones in memory and infer multiple patterns in the access stream. To make accurate predictions, it uses a bitmap-like data structure to hold the information of memory accesses occurred in the recent past. Next, it divides the memory address space into memory regions of a fixed size and relates the memory access map to each region. Finally, it makes use of pattern matching logic for inferring memory access patterns in each mapped region, detecting all possible strides at the same time. With the detected patterns, it predicts future memory accesses independently of the order in which they are observed, in turn attaining a high prefetch coverage.

By recognizing that temporal address correlation often allows the detection of complex memory access patterns with higher accuracy, Global History Buffers (GHBs) [31, 33] were introduced to represent a temporal address history. They hold the most recent memory accesses in a First-In Variable Length Delta Prefetcher (Shevgoor et al. 2015)

Figure 2.6: Temporal-based prefetching mechanism of the VLDP prefetcher [32].

First-Out (FIFO) buffer and use a linked list to store the sequence of accessed addresses. However, although being more efficient than prediction tables, in some cases it may involve a large number of sequential accesses and modifications to the linked list, resulting in long latency in the prediction of the addresses to be prefetched.

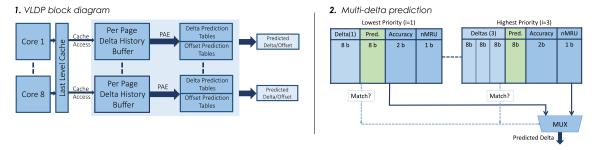

To mitigate such issues, GHBs are often combined with other prediction structures, allowing researchers to efficiently exploit the history of accesses to calculate accurate future accesses [21, 32]. As an example, Shevgoor et al. [32] proposed the Variable Length Delta Prefetcher (VLDP). It maintains local delta (stride) histories for each physical page accessed by a given workload in multiple delta history buffers with different lengths. When a prefetching opportunity is detected in one of the tracked pages, its delta history is used to perform lookups in delta prediction tables (see Fig. 2.6) to infer the correct prefetches to issue. The utilization of multiple prediction tables (corresponding to different history lengths), allows the VLDP to maximize prefetch coverage and accuracy, by preferring to use long histories to make accurate prefetches and using shorter histories to fill in the gaps when long histories are unavailable.

# 2.2.2.C Irregular and Correlation Prefetching

Since spatial and temporal prefetching rely on the assumption that accesses maintain a certain regularity over time, they fall short when the memory access is not sequential or presents some degree of irregularity. Hence, to deal with such situations, temporal and spatial correlation heuristics have been deployed in some prefetchers. They usually deploy probabilistic and automatic learning algorithms that analyze the recent address history and, instead of calculating differences, identify regions of interest in the memory to be prefetched. As an example, in [55] it is introduced a context-based memory prefetcher, which approximates spatial and temporal locality by applying reinforced learning methods over system and code attributes, which provide valuable hints for memory access prediction.

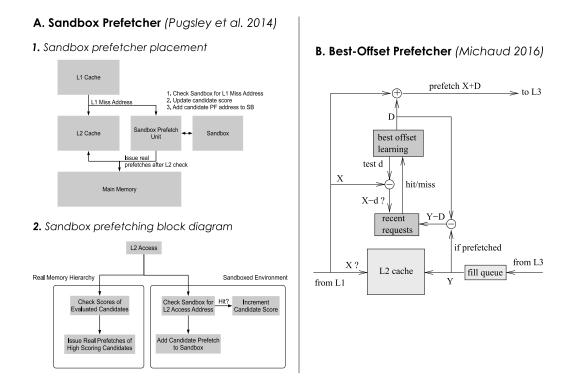

Recently, Pugsley et al. [23] introduced a new category of offset prefetchers, as a generalization of the classic next-line prefetching, supported by a sandbox method to dynamically select the prefetch offset (see Fig. 2.7.A). It works on the principle of validating the accuracy of the

Figure 2.7: Schematic views of (A) the Sandbox Prefetcher [23] and (B) the Best-Offset Prefetcher [22].

prefetchers in a safe, sandbox environment, where neither the real cache nor memory bandwidth is disturbed. To do so, the proposed method issues "fake" prefetch requests by recording them in a bloom filter structure and calculating their accuracy by checking if a subsequent access hits in the bloom filter. The actual prefetch candidates are then deployed in the real memory hierarchy only if they prove that they can accurately prefetch useful data.

Following the same principle, Michaud [22] proposed the Best-Offset Prefetcher. It was designed with prefetching timeliness in mind and implements an offset selection mechanism that dynamically sets the prefetching offset depending on the application behavior to maximize prefetch coverage (see Fig. 2.7.B). This mechanism relies on a best-offset learning algorithm that tries to find the best prefetch offset by testing several different offsets. It does so by recording the base address of prefetch requests that have been completed in a recent requests table and inferring the correct timeliness for a prefetch candidate based on how recently a cache line was accessed.

Due to its detachment from spatial and temporal locality, address correlation is also adopted to deal with irregular applications (such as data-based accesses, graph- and list-oriented and pointer-based applications). To deal with the irregular nature of graph structures, Zhang et al. [17] proposed a worklist-directed prefetching technique, that takes advantage of the processing system's knowledge of upcoming work items to issue prefetch requests accurately. The prefetcher is paired with a credit-based system to improve prefetch timeliness and prevent cache thrashing. Jain et al. [19] proposed a structural address space that translates arbitrary pairs of correlated physical addresses into consecutive addresses. This allows their proposed Irregular Stream Buffer (ISB) to organize prefetching meta-data so that it is simultaneously temporally and spatially ordered.

#### 2.2.2.D Compiler-aided Prefetching

Although predictive approaches allow a high abstraction of the application from the prefetching procedure, they can fall short when the application is characterized by complex memory access patterns. Moreover, they impose an increased amount of resources, often related to the adopted level of prefetching aggressiveness [18, 23].

Hence, alternative solutions have been considered [18, 53] that rely on compile-time procedures, where the compiler pre-analyzes the code and tries to extract/model the application memory access pattern. Such information is then fed to on-chip prefetching modules, mitigating the effort of their prediction procedures. By eliminating unnecessary requests, these approaches reduce the prediction overheads while also improving the accuracy of the prefetchers. They also lead to far simpler hardware structures, since no runtime analysis is performed, in turn resulting in lower-footprint and more energy efficient controllers, at the cost of an increased pre-processing effort.

Ebrahimi et al. [53] explored such an approach, through a hardware/software cooperative technique for the prefetching of linked data structures. They proposed a compiler-guided prefetch filtering mechanism that informs the hardware about which pointer addresses to prefetch, and a prefetch throttling mechanism that relies on runtime feedback to manage the operation of multiple prefetching architectures. Another example is the Power-Aware pRefetch Engine (PARE) [18], a compiler-assisted prefetching mechanism, which utilizes compiler information to selectively apply different hardware prefetching schemes based on predicted memory access patterns. It also applies filtering techniques at compile-time and at runtime to reduce the number of accesses to be prefetched by hardware, consequently reducing the L1 cache related energy overhead due to prefetching.

# 2.2.3 Data Streaming Architectures

Despite the high accuracy provided by current prefetching approaches, their predictive nature and necessary runtime monitoring impose inevitable inaccuracies and delays in the memory access infrastructure. In particular, while the prediction delays are inevitable to maximize accuracy and coverage in such scenarios, an increased amount of resources is required, often increasing the system's overall energy consumption [18]. Moreover, even the most sophisticated techniques are not well-suited to processing systems with large numbers of processing cores, due to possible contention introduced in the shared interconnections caused by massive on-the-fly prefetch requests. Such contention may even degrade the system's throughput to the point where the

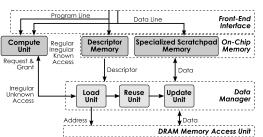

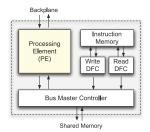

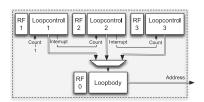

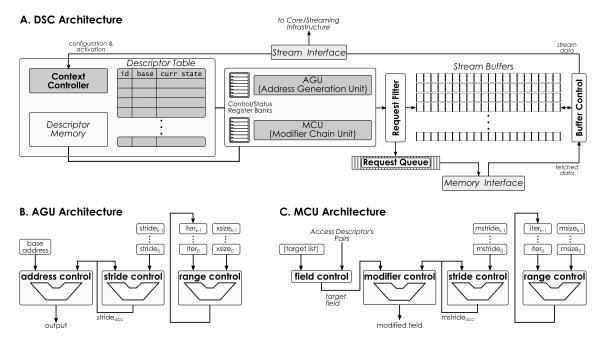

# Advanced Pattern-based Memory Controller (Hussain et al. 2014)

#### 1. APMC block diagram

2. APMC descriptor blocks

| Regular / Irregular Descriptor |                  |                     |      | Irregular |      |      |

|--------------------------------|------------------|---------------------|------|-----------|------|------|

| Command                        | Local<br>Address | External<br>Address | Size | Stride    | Туре | Next |

|                                |                  |                     |      |           |      |      |