UNIFY Project

Unifying General-Purpose and Specilized Computing

Funded with National Funds from

FCT: 2022.06780.PTDC

(DOI:10.54499/2022.06780.PTDC)

Context

Computing Domain Fragmentation

The ever-increasing amount of data availability and the consequent algorithmic advances have increased the awareness about the performance and efficiency limitations of current General-Purpose Processors (GPPs). In fact, a further increase of transistor density and size miniaturization, conventionally adopted until now to push performance, is becoming less viable, as CMOS technology is reaching its limit. As a result, a gradual stagnation has been observed in the development of new GPP architectures, opening the space for the exploration of architectural specialization as an economically viable solution to cope with the current challenges for energy-efficient computing. This new specialization trend has shifted the computing paradigm to a new class of Domain-Specific Architectures (DSAs). These accelerators often rely on unconventional mechanisms/techniques that are usually deemed unfit for GPPs, such as data streaming and reconfigurable technologies. This has had a significant impact on algorithm development and on the programming environment. In fact, there is a growing concern that specialization will fragment the computing market in upcoming years, as too much attention is being given to prominent application domains while many areas that rely on GPPs are becoming stagnated. This will keep the existing GPPs inefficiencies unsolved, while DSAs will only push innovation in very specific areas. Moreover, the increasing number of DSLs introduces a development overhead for each application domain that may turn out impractical for general users.

Main Goals

Unifying General-Purpose and Specilized Computing

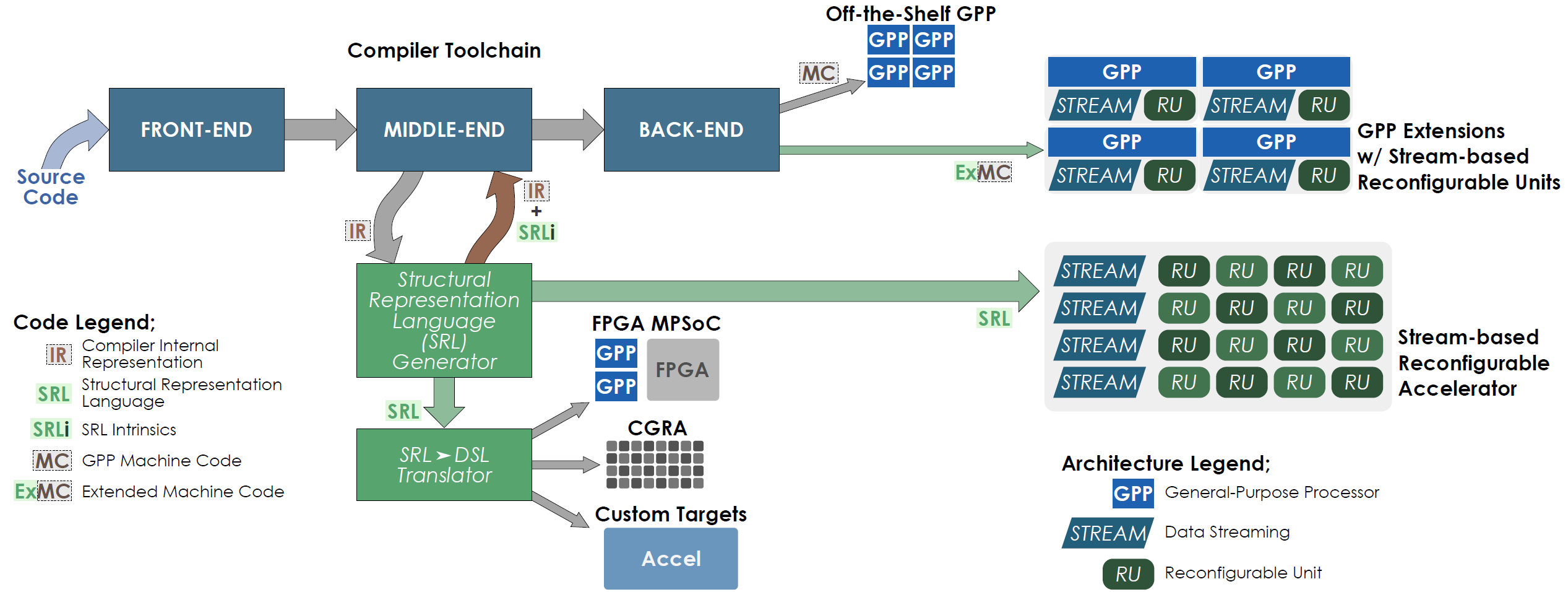

The simultaneous adoption of new compiler technologies and new architecture innovations has been recognized as the most prominent alternative to avoid this foreseeable fragmentation between specialized and general-purpose computing. Accordingly, the main objective of this project is to tackle this ambitious challenge, by recognizing that the starting steps towards a unification of these paradigms lie in extending compilation tools to abstract the application structural information from the characteristics of the underlying hardware. Accordingly, a new Structural Representation Language (SRL) specification shall be proposed to allow the automatic detection and representation of deterministic and non-deterministic computing structures and memory access schemes. The development of the envisaged SRL will be complemented with the deployment of an open-source framework comprising new compiler extensions to infer SRL constructs from the compiler's internal representation language. Such constructs will be then translated back either to general-purpose machine-code, accelerator code, or for mapping to DSL constructs (targeting DSAs). Such a new SRL (and corresponding compilation framework) will exploit the information gathered during compilation to support the definition and adaptation of the underlying reconfigurable processing architectures supported by data streaming schemes (deployed either as functional units within a general-purpose pipeline or as co-accelerators within a heterogeneous computing platform), thus promoting runtime domain-specific specialization, resource management, and performance and energy consumption balancing. Although achieving a true unification is challenging and possibly still several years away, this project aims at taking significant steps in that direction, by deploying a fully functional computing ecosystem that not only provides a new abstraction layer between specialized and general-purpose computing, but that also aims at attaining significant performance boosts while reducing energy consumption.

Research Team Overview

To attain this challenging goal, this project joins together a set of researches from three Portuguese renowned research institutes with proven experience in the design of processor and accelerator architectures, data streaming mechanisms, reconfigurable systems, compiler tools and application modelling.